Opteron

It was released on April 22, 2003, with the SledgeHammer core (K8) and was intended to compete in the server and workstation markets, particularly in the same segment as the Intel Xeon processor.

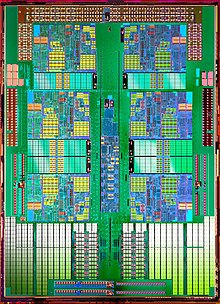

Processors based on the AMD K10 microarchitecture (codenamed Barcelona) were announced on September 10, 2007, featuring a new quad-core configuration.

The second capability, by itself, is less noteworthy, as major RISC architectures (such as SPARC, Alpha, PA-RISC, PowerPC, MIPS) have been 64-bit for many years.

In combining these two capabilities, however, the Opteron earned recognition for its ability to run the vast installed base of x86 applications economically, while simultaneously offering an upgrade path to 64-bit computing.

This both reduces the latency penalty for accessing the main RAM and eliminates the need for a separate northbridge chip.

In multi-processor systems (more than one Opteron on a single motherboard), the CPUs communicate using the Direct Connect Architecture over high-speed HyperTransport links.

In particular, the Opteron's integrated memory controller allows the CPU to access local RAM very quickly.

In contrast, multiprocessor Xeon system CPUs share only two common buses for both processor-processor and processor-memory communication.

As the number of CPUs increases in a typical Xeon system, contention for the shared bus causes computing efficiency to drop.

At the time, AMD's use of the term multi-core in practice meant dual-core; each physical Opteron chip contained two processor cores.

At the time of its introduction, AMD's fastest multicore Opteron was the model 875, with two cores running at 2.2 GHz each.

AMD's fastest single-core Opteron at this time was the model 252, with one core running at 2.6 GHz.

Based on a core design codenamed Barcelona, new power and thermal management techniques were planned for the chips.

It introduced HT Assist, an additional directory for data location, reducing the overhead for probing and broadcasts.

Opteron 4000 series CPUs on Socket C32 (released July 2010) are dual-socket capable and are targeted at uniprocessor and dual-processor uses.

The Opteron 6000 series CPUs on Socket G34 are quad-socket capable and are targeted at high-end dual-processor and quad-processor applications.

AMD released Socket 939 Opterons, reducing the cost of motherboards for low-end servers and workstations.

Except for the fact they have 1 MB L2 cache (versus 512 KB for the Athlon 64) the Socket 939 Opterons are identical to the San Diego and Toledo core Athlon 64s, but are run at lower clock speeds than the cores are capable of, making them more stable.

the "lidded land grid array" socket adds support for DDR2 SDRAM and improved HyperTransport version 3 connectivity.

New processors, launched in the third quarter of 2007 (codename Barcelona), incorporate a variety of improvements, particularly in memory prefetching, speculative loads, SIMD execution and branch prediction, yielding an appreciable performance improvement over K8-based Opterons, within the same power envelope.

The suffix SE indicates a top-of-the-line model having a higher TDP than a standard Opteron.

Starting from 65 nm fabrication process, the Opteron codenames have been based on Formula 1 hosting cities; AMD has a long term sponsorship with F1's most successful team, Ferrari.

[12][13] Released June, 2017 Opteron processors first appeared in the top 100 systems of the fastest supercomputers in the world list in the early 2000s.

The following table describes affected processors, as listed in AMD Opteron ×52 and ×54 Production Notice of 2006.