Interrupt

[2] Interrupts are commonly used by hardware devices to indicate electronic or physical state changes that require time-sensitive attention.

[5][6] Earlier, on the UNIVAC I (1951) "Arithmetic overflow either triggered the execution of a two-instruction fix-up routine at address 0, or, at the programmer's option, caused the computer to stop."

The IBM 704 was the first to use interrupts for debugging, with a "transfer trap", which could invoke a special routine when a branch instruction was encountered.

The MIT Lincoln Laboratory TX-2 system (1957) was the first to provide multiple levels of priority interrupts.

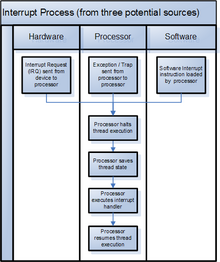

A hardware interrupt is a condition related to the state of the hardware that may be signaled by an external hardware device, e.g., an interrupt request (IRQ) line on a PC, or detected by devices embedded in processor logic (e.g., the CPU timer in IBM System/370), to communicate that the device needs attention from the operating system (OS)[7] or, if there is no OS, from the bare metal program running on the CPU.

Hardware interrupts can arrive asynchronously with respect to the processor clock, and at any time during instruction execution.

Consequently, all incoming hardware interrupt signals are conditioned by synchronizing them to the processor clock, and acted upon only at instruction execution boundaries.

[10] One failure mode is when the hardware does not generate the expected interrupt for a change in state, causing the operating system to wait indefinitely.

A spurious interrupt may also be the result of electrical anomalies due to faulty circuit design, high noise levels, crosstalk, timing issues, or more rarely, device errata.

[e] Such instructions function similarly to subroutine calls and are used for a variety of purposes, such as requesting operating system services and interacting with device drivers (e.g., to read or write storage media).

Software interrupts may also be triggered by program execution errors or by the virtual memory system.

In some usages, the term trap refers specifically to a breakpoint intended to initiate a context switch to a monitor program or debugger.

A device invokes a level-triggered interrupt by driving the signal to and holding it at the active level.

Level-triggered inputs allow multiple devices to share a common interrupt signal via wired-OR connections.

Many older devices assume that they have exclusive use of IRQ lines, making it electrically unsafe to share them.

Accumulators only trigger when the remote side excites the gate beyond a threshold, thus no negotiated speed is required.

Some devices with a poorly designed programming interface provide no way to determine whether they have requested service.

Such devices are becoming much rarer, as hardware logic becomes cheaper and new system architectures mandate shareable interrupts.

The hardware not only looks for an edge, but it also verifies that the interrupt signal stays active for a certain period of time.

Instead, a device signals its request for service by sending a short message over some communications medium, typically a computer bus.

It is this act of writing to the doorbell region of memory that "rings the bell" and notifies the hardware device that the data are ready and waiting.

It would typically write the data to a hard disk drive, or send them over a network, or encrypt them, etc.

There are various forms of livelocks, when the system spends all of its time processing interrupts to the exclusion of other required tasks.

Under extreme conditions, a large number of interrupts (like very high network traffic) may completely stall the system.

[24] With multi-core processors, additional performance improvements in interrupt handling can be achieved through receive-side scaling (RSS) when multiqueue NICs are used.

Advantages of RPS over RSS include no requirements for specific hardware, more advanced traffic distribution filters, and reduced rate of interrupts produced by a NIC.

[25][27][28] Interrupts are commonly used to service hardware timers, transfer data to and from storage (e.g., disk I/O) and communication interfaces (e.g., UART, Ethernet), handle keyboard and mouse events, and to respond to any other time-sensitive events as required by the application system.

Non-maskable interrupts are typically used to respond to high-priority requests such as watchdog timer timeouts, power-down signals and traps.

Periodic interrupts are also commonly used to invoke sampling from input devices such as analog-to-digital converters, incremental encoder interfaces, and GPIO inputs, and to program output devices such as digital-to-analog converters, motor controllers, and GPIO outputs.

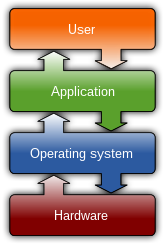

The kernel may pass an interrupt as a signal to the process that caused it (typical examples are SIGSEGV, SIGBUS, SIGILL and SIGFPE).