Page table

The page table is a key component of virtual address translation that is necessary to access data in memory.

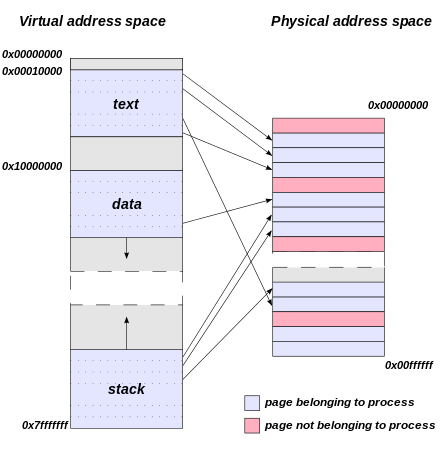

Physically, the memory of each process may be dispersed across different areas of physical memory, or may have been moved (paged out) to secondary storage, typically to a hard disk drive (HDD) or solid-state drive (SSD).

When a process requests access to data in its memory, it is the responsibility of the operating system to map the virtual address provided by the process to the physical address of the actual memory where that data is stored.

[1][2] The memory management unit (MMU) inside the CPU stores a cache of recently used mappings from the operating system's page table.

If a match is found, which is known as a TLB hit, the physical address is returned and memory access can continue.

However, if there is no match, which is called a TLB miss, the MMU, the system firmware, or the operating system's TLB miss handler will typically look up the address mapping in the page table to see whether a mapping exists, which is called a page walk.

The TLB also needs to be updated, including removal of the paged-out page from it, and the instruction restarted.

Secondary storage, such as a hard disk drive, can be used to augment physical memory.

When a dirty bit is not used, the backing store need only be as large as the instantaneous total size of all paged-out pages at any moment.

When a dirty bit is used, at all times some pages will exist in both physical memory and the backing store.

An inverted page table (IPT) is best thought of as an off-chip extension of the TLB which uses normal system RAM.

Depending on the architecture, the entry may be placed in the TLB again and the memory reference is restarted, or the collision chain may be followed until it has been exhausted and a page fault occurs.

A major problem with this design is poor cache locality caused by the hash function.

An operating system may minimize the size of the hash table to reduce this problem, with the trade-off being an increased miss rate.

It is somewhat slow to remove the page table entries of a given process; the OS may avoid reusing per-process identifier values to delay facing this.

[4] The inverted page table keeps a listing of mappings installed for all frames in physical memory.

By providing hardware support for page-table virtualization, the need to emulate is greatly reduced.