Pixel Visual Core

The Pixel Visual Core (PVC) is a series of ARM-based system in package (SiP) image processors designed by Google.

[1] The PVC is a fully programmable image, vision and AI multi-core domain-specific architecture (DSA) for mobile devices and in future for IoT.

Google claims the PVC uses less power than using CPU and GPU while still being fully programmable, unlike their tensor processing unit (TPU) application-specific integrated circuit (ASIC).

Currently, it supports just a subset of Halide programming language without floating point operations and with limited memory access patterns.

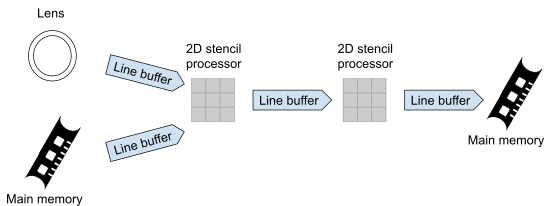

The STP mainly provides a 2-D SIMD array of processing elements (PEs) able to perform stencil computations, a small neighborhood of pixels.

[2] Considering that one of the most energy costly operation is DRAM access, each STP has temporary buffers to increase data locality, namely LBP.

[8] Due to the real high complexity of the memory system, the PVC designers state the LBP controller as one of the most challenging components.

[2] The NoC used is a ring network on chip used to communicate with only neighbor cores for energy savings and pipelined computational pattern preservation.

[2] The SR3HX PVC features a 64-bit ARMv8a ARM Cortex-A53 CPU, 8x image processing unit (IPU) cores, 512 MB LPDDR4, MIPI, PCIe.

The IPU cores each have 512 arithmetic logic units (ALUs) consisting of 256 processing elements (PEs) arranged as a 16 x 16 2-dimensional array.