Intel 8086

The 8086[3] (also called iAPX 86)[4] is a 16-bit microprocessor chip designed by Intel between early 1976[citation needed] and June 8, 1978, when it was released.

[5] The Intel 8088, released July 1, 1979,[6] is a slightly modified chip with an external 8-bit data bus (allowing the use of cheaper and fewer supporting ICs),[note 1] and is notable as the processor used in the original IBM PC design.

[note 2] It implemented an instruction set designed by Datapoint Corporation with programmable CRT terminals in mind, which also proved to be fairly general-purpose.

Two years later, Intel launched the 8080, employing the new 40-pin DIL packages originally developed for calculator ICs to enable a separate address bus.

The 8080 device was eventually replaced by the depletion-load-based 8085 (1977), which used a single +5 V power supply instead of the three different operating voltages of earlier chips.

Instructions were added to assist source code compilation of nested functions in the ALGOL-family of languages, including Pascal and PL/M.

The first revision of the instruction set and high level architecture was ready after about three months,[note 4] and as almost no CAD tools were used, four engineers and 12 layout people were simultaneously working on the chip.

The 8086 was sequenced[note 6] using a mixture of random logic[9] and microcode and was implemented using depletion-load nMOS circuitry with approximately 20,000 active transistors (29,000 counting all ROM and PLA sites).

Logic designer Jim McKevitt and John Bayliss were the lead engineers of the hardware-level development team[note 9] and Bill Pohlman the manager for the project.

The maximum linear address space is limited to 64 KB, simply because internal address/index registers are only 16 bits wide.

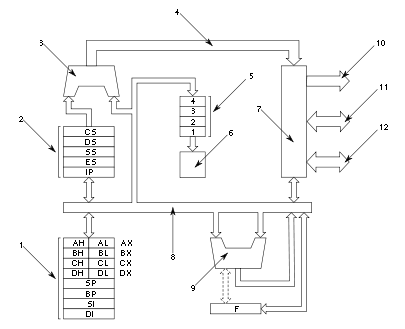

Four of them, AX, BX, CX, DX, can also be accessed as 8-bit register pairs (see figure) while the other four, SI, DI, BP, SP, are 16-bit only.

Due to a compact encoding inspired by 8-bit processors, most instructions are one-address or two-address operations, which means that the result is stored in one of the operands.

A single memory location can also often be used as both source and destination which, among other factors, further contributes to a code density comparable to (and often better than) most eight-bit machines at the time.

While perfectly sensible for the assembly programmer, this makes register allocation for compilers more complicated compared to more orthogonal 16-bit and 32-bit processors of the time such as the PDP-11, VAX, 68000, 32016, etc.

On the other hand, being more regular than the rather minimalistic but ubiquitous 8-bit microprocessors such as the 6502, 6800, 6809, 8085, MCS-48, 8051, and other contemporary accumulator-based machines, it is significantly easier to construct an efficient code generator for the 8086 architecture.

Although considered complicated and cumbersome by many programmers, this scheme also has advantages; a small program (less than 64 KB) can be loaded starting at a fixed offset (such as 0000) in its own segment, avoiding the need for relocation, with at most 15 bytes of alignment waste.

The tiny model means that code and data are shared in a single segment, just as in most 8-bit based processors, and can be used to build .com files for instance.

The queue acts as a First-In-First-Out (FIFO) buffer, from which the Execution Unit (EU) extracts instruction bytes as required.

The authors of most DOS implementations took advantage of this by providing an Application Programming Interface very similar to CP/M as well as including the simple .com executable file format, identical to CP/M.

This was important when the 8086 and MS-DOS were new, because it allowed many existing CP/M (and other) applications to be quickly made available, greatly easing acceptance of the new platform.

The example code uses the BP (base pointer) register to establish a call frame, an area on the stack that contains all of the parameters and local variables for the execution of the subroutine.

Although partly shadowed by other design choices in this particular chip, the multiplexed address and data buses limit performance slightly; transfers of 16-bit or 8-bit quantities are done in a four-clock memory access cycle, which is faster on 16-bit, although slower on 8-bit quantities, compared to many contemporary 8-bit based CPUs.

Combined with orthogonalizations of operations versus operand types and addressing modes, as well as other enhancements, this made the performance gain over the 8080 or 8085 fairly significant, despite cases where the older chips may be faster (see below).

The 80C86, the CMOS version of the 8086, was used in many portable computers and embedded systems, including the GridPad, Toshiba T1200, HP 110, and finally the 1998–1999 Lunar Prospector.