Memory address

[1] These addresses are fixed-length sequences of digits, typically displayed and handled as unsigned integers.

This numerical representation is based on the features of CPU (such as the instruction pointer and incremental address registers), as well programming language constructs that treat the memory like an array.

Generally, only system software (such as the BIOS, operating systems, and specialized utility programs like memory testers) directly addresses physical memory using machine code instructions or processor registers.

The bus managed by the memory controller consists of multiple parallel lines, each representing a binary digit (bit).

A computer program uses memory addresses to execute machine code, and to store and retrieve data.

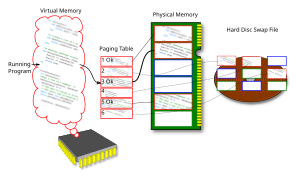

However, with the introduction of virtual memory most application programs do not deal directly with physical addresses.

There exist word-addressable computers, where the minimal addressable storage unit is exactly the processor's word.

Word size is a characteristic of computer architecture denoting the number of bits that a CPU can process at one time.

For instance, many 8-bit processors, such as the MOS Technology 6502, supported 16-bit addresses— if not, they would have been limited to a mere 256 bytes of memory addressing.

Many early LISP implementations on, e.g., 36-bit processors, held 2 addresses per word as the result of a cons.

Self-modifying code is generally deprecated nowadays, as it makes testing and maintenance disproportionally difficult to the saving of a few bytes, and can also give incorrect results because of the compiler or processor's assumptions about the machine's state, but is still sometimes used deliberately, with great care.

Some systems have a "split" memory architecture where machine code, constants, and data are in different locations, and may have different address sizes.

Mapping logical addresses to physical and virtual memory also adds several levels of indirection; see below.

z/Architecture supports 64-bit virtual, real and absolute addresses, with multi-level page tables.