Content-addressable memory

[1] CAM is frequently used in networking devices where it speeds up forwarding information base and routing table operations.

A similar concept can be found in the data word recognition unit, as proposed by Dudley Allen Buck in 1955.

The extra circuitry also increases power dissipation since every comparison circuit is active on every clock cycle.

[5] In the early 2000s several semiconductor companies including Cypress, IDT, Netlogic, Sibercore,[6] and MOSAID introduced CAM products targeting networking applications.

[7] To achieve a different balance between speed, memory size and cost, some implementations emulate the function of CAM by using standard tree search or hashing designs in hardware, using hardware tricks like replication or pipelining to speed up effective performance.

[citation needed] The Luleå algorithm is an efficient implementation for longest prefix match searches as required in internet routing tables.

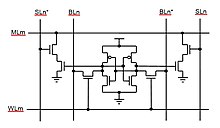

Ternary CAM (TCAM)[8] allows a third matching state of X or don't care for one or more bits in the stored word, thus adding flexibility to the search.

[9] A design of TCAM using hybrid Ferroelectric FeFET was recently published by a group of International scientists.

The MAC address table is usually implemented with a binary CAM so the destination port can be found very quickly, reducing the switch's latency.