Dadda multiplier

The Dadda multiplier is a hardware binary multiplier design invented by computer scientist Luigi Dadda in 1965.

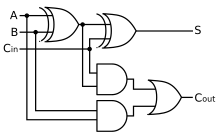

[1] It uses a selection of full and half adders to sum the partial products in stages (the Dadda tree or Dadda reduction) until two numbers are left.

The design is similar to the Wallace multiplier, but the different reduction tree reduces the required number of gates (for all but the smallest operand sizes) and makes it slightly faster (for all operand sizes).

[2] Dadda and Wallace multipliers have the same three steps for two bit strings

ℓ

ℓ

respectively: As with the Wallace multiplier, the multiplication products of the first step carry different weights reflecting the magnitude of the original bit values in the multiplication.

For example, the product of bits

Unlike Wallace multipliers that reduce as much as possible on each layer, Dadda multipliers attempt to minimize the number of gates used, as well as input/output delay.

Because of this, Dadda multipliers have a less expensive reduction phase, but the final numbers may be a few bits longer, thus requiring slightly bigger adders.

To achieve a more optimal final product, the structure of the reduction process is governed by slightly more complex rules than in Wallace multipliers.

The progression of the reduction is controlled by a maximum-height sequence

, defined by: This yields a sequence like so: The initial value of

is chosen as the largest value such that

< min

are the number of bits in the input multiplicand and multiplier.

The lesser of the two bit lengths will be the maximum height of each column of weights after the first stage of multiplication.

of the reduction, the goal of the algorithm is the reduce the height of each column so that it is less than or equal to the value of

, reduce each column starting at the lowest-weight column,

according to these rules: The example in the adjacent image illustrates the reduction of an 8 × 8 multiplier, explained here.

The initial state

is chosen as

, the largest value less than 8.

Addition The output of the last stage leaves 15 columns of height two or less which can be passed into a standard adder.