MIPI Debug Architecture

In recent years, the group focused on specifying protocols that improve the visibility of the internal operations of deeply embedded systems, standardizing debug solutions via the functional interfaces of form factor devices, and specifying the use of I3C as debugging bus.

[1][2] The term "debug" encompasses the various methods used to detect, triage, trace, and potentially eliminate mistakes, or bugs, in hardware and software.

In stop/step mode debugging, the core/microcontroller is stopped through the use of breakpoints and then "single-stepped" through the code by executing instructions one at a time.

Stop/step mode debugging includes control/configure techniques, run control of a core/microcontroller, start/stop synchronization with other cores, memory and register access, and additional debug features such as performance counter and run-time memory access.

The generation of system trace data from the software is typically done by inserting additional function calls, which produce diagnostic information valuable for the debug process.

The translation from the numeric value to a message string is done by the trace analysis tool, with the help of collateral XML information.

This information is provided during the software-build process using an XML schema that is part of the specification as well.

SyS-T protocol features such as timestamping or data-integrity checksums can be disabled if the transport link already provides such capabilities.

ARM's CoreSight System Trace Macrocell,[4] which is compliant with MIPI STP, is today an integral part of most multi-core chips used in the mobile space.

The MIPI Debug Architecture provides specifications for both parallel and serial trace ports.

[7] The MIPI High-Speed Trace Interface (MIPI HTI) specifies how to stream trace data over the physical layer of standard interfaces, such as PCI Express, DisplayPort, HDMI, or USB.

Seven different pin mappings that address a wide variety of debug scenarios have been specified.

Many embedded designs in the mobile space use high-speed parallel trace ports (up to 600 megabits per second per pin).

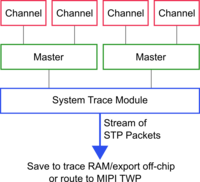

To minimize complexity, the recommendation defines four standard configurations with one, two, three, or four trace channels of varying width.

Since the debug logic is still present in the end product, an alternative access path is needed.

An effective way is to equip a mobile terminal's standard interface with a multiplexer that allows for accessing the debug logic.

[12] Instead of re-using the pins, debugging can also be done via the protocol stack of a standard interface or network.