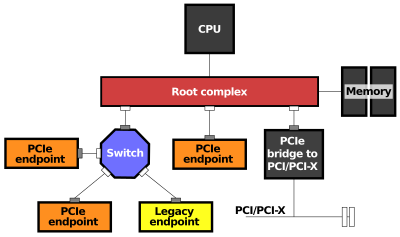

Root complex

[2] The root complex generates transaction requests on behalf of the CPU, which is interconnected through a local bus.

[3][4] The PCIe Root Complex holds a master copy of a 'Type 1 Configuration Table' that defines the host memory space that is accessible from each Endpoint device.

In addition, each PCIe Endpoint device holds a master copy of their own memory space map in the host system memory as a 'Type 0 Configuration Table', this configuration table in each device allows the host to access the local memory of a PCIe device.

Both the Type 1 and Type 0 configuration tables are set up by the Host Operating System that controls the Root Complex by a process known as enumeration and which acts to build a device memory map for the system by querying each bridge, and endpoint device connected on the bus network.

Similarly, a PCIe Bridge acts a tiered root complex with a "Type 0 Configuration Table".