TMS9900

[a] Introduced in June 1976, it implemented Texas Instruments's TI-990 minicomputer architecture in a single-chip format, and was initially used for low-end models of that lineup.

The 9900 architecture lived on into the 1990s as the Communications Processor in TI's TMS380 chipset for Token Ring networking (later Ethernet).

The minicomputer roots of the TMS9900 give rise to a number of architectural features that are not commonly found on designs that started from a blank sheet.

More traditional designs would require the entire set of internal registers to be stored out to memory or the stack.

In a minicomputer implementation with fast memory, the effect is relatively small and the upside in a real-time or multi-tasking environment is significant as context switches are common.

In the late 1970s Walden C. Rhines gave a presentation of the TMS99110, then code-named "Alpha",[3] to an IBM group developing a personal computer.

After dropping out of the personal computer market after products such as TI-99/4A, the company microprocessor division eventually switched focus to the TMS320 special-purpose processor series.

[7] The WP points to a base address in external RAM where 16 general purpose user registers (each 16 bits wide) reside to serve the processor.

Using BLWP/RTWP, it is possible to nest subroutine calls despite the absence of a stack, however, the programmer needs to assign the appropriate register workspace explicitly.

The instruction set also contains a Branch and Link (BL) opcode that only saves PC to register 11 without changing WP.

[9] XOP is less flexible than a BLWP, as the transfer vectors have to be at fixed locations, but allows one source operand to be directly addressed rather than passed in a register or otherwise.

Another use of XOP was to implement instructions in software which might be handled by dedicated hardware in future versions of the 990 minicomputer series.

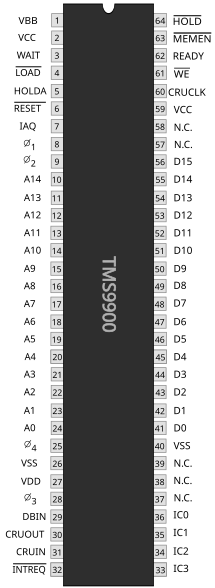

The TMS9900 was implemented in an N-channel silicon gate MOS process,[7] which required +5 V, −5 V and +12 V power supplies and a four-phase (non-overlapping) clock with a maximum frequency of 3 MHz (333 ns cycle),[10] usually generated from a 48 MHz crystal using a TIM9904 (aka 74LS362) clock generator chip.

Like Motorola, contrary to the convention used by many other manufacturers, TI labeled the most significant address and data lines "A0" and "D0," respectively.

The processor can be paused with the address bus tri-stated for external direct memory access (DMA).

Unfortunately, to reduce the production costs, TI chose to use just 256 bytes (128 16-bit words) of the fast kind of RAM that the TMS9900 could access directly.

The rest of the memory was 16 KB of 8-bit DRAM that was accessible only indirectly through the video display controller, which crippled the performance of these machines.

TI developed the TM990 series of computer modules, including CPU, memory, and I/O, which, when plugged into a card frame, could form a 16-bit minicomputer.

[14] In the late 1970s, John Walker and Dan Drake developed S100-bus cards based on the TMS9900 and a full software stack to go with it.

[17] The next generation of the TMS9900 was the TMS9995, which provided "functional performance at speeds three times faster than any previous 9900 family processor,"[18] largely due to the inclusion of instruction prefetch technology.

In the home computer arena, the TMS9995 only found use in the Tomy Tutor, as well as an obscure third-party computer-on-a-card upgrade for the TI-99/4A called the Geneve 9640, and a project printed in Electronics Today: the Powertran Cortex.