Time-to-digital converter

This pattern is seen in many physical experiments, like time-of-flight and lifetime measurements in atomic and high energy physics, experiments that involve laser ranging and electronic research involving the testing of integrated circuits and high-speed data transfer.

[2][3] In an all-digital phase-locked loop (ADPLL), a TDC measures the phase shift and its result is used to adjust the digital controlled oscillator (DCO).

In its simplest implementation, a TDC is simply a high-frequency counter that increments every clock cycle.

Typically a TDC uses a crystal oscillator reference frequency for good long term stability.

High stability crystal oscillators are usually relative low frequency such as 10 MHz (or 100 ns resolution).

This allows designers to peak the device for a specific frequency, which may lie above the cut-off-frequency of the original transistor.

Other methods to achieve sub-cycle resolution include analog-to-digital converters and vernier Johnson counters.

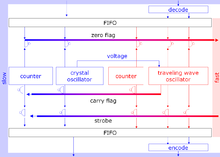

Coarse counters base on a reference clock with signals generated at a stable frequency

This detuning of the start and stop signal from the clock pulses is called quantization error.

In comparison to the other methods described later on, a coarse counter has a very limited resolution (1 ns in case of a 1 GHz reference clock), but satisfies with its theoretically unlimited measuring range.

In contrast to the coarse counter in the previous section, fine measurement methods with much better accuracy (picosecond resolution?

Though the analogue methods still obtain better accuracies, digital time interval measurement is often preferred due to its flexibility in integrated circuit technology and its robustness against external perturbations like temperature changes.

The interpolation circuits often require a significant amount of time to perform their function; consequently, the TDC needs a quiet interval before the next measurement.

The voltage on the capacitor v is directly proportional to the time interval T and can be measured with an analog-to-digital converter (ADC).

The dual-slope conversion can take a long time: a thousand or so clock ticks in the scheme described above.

Resolution of 1 ps with a 100 MHz (10 ns) clock requires a stretch ratio of 10,000 and implies a conversion time of 150 μs.

[9][11] For convenience, imagine that the fast ramp rises exactly 1 volt during a 100 ns clock period.

After 1327 clocks, the slow ramp returns to its starting point, and interpolator knows that the event occurred 132.7 ns before the synchronizer reported.

The basic idea has some complications: the start and stop events are asynchronous, and one or both might happen close to a clock pulse.

The first direct predecessor of a TDC was invented in the year 1942 by Bruno Rossi for the measurement of muon lifetimes.

Starting with vacuum tubes and ferrite pot-core transformers those ideas are implemented in complementary metal–oxide–semiconductor (CMOS) design today.

Non-linearities of the time-to-digital conversion for example can be identified by taking a large number of measurements of a poissonian distributed source (statistical code density test).

Inconveniently the statistical code density method is quite sensitive to external temperature changes.

For long time intervals, the error due to instabilities in the reference clock (jitter) plays a major role.

[24] TDCs are currently built as stand-alone measuring devices in physical experiments or as system components like PCI cards.

It is this fast clock that is gated by the (fine-delayed) start event and determines the main quantization error.

Just as a TDC may use interpolation to get finer than one clock period resolution, a delay generator may use similar techniques.

The Hewlett-Packard 5359A High Resolution Time Synthesizer provides delays of 0 to 160 ms, has an accuracy of 1 ns, and achieves a typical jitter of 100 ps.

The delay generator can be used for pulse-width modulation, e.g. to drive a MOSFET to load a Pockels cell within 8 ns with a specific charge.

If a series of DACs is gated in sequence, variable pulse shapes can be generated to account for any transfer function.