Zen (first generation)

[4] The first Zen-based preview system was demonstrated at E3 2016, and first substantially detailed at an event hosted a block away from the Intel Developer Forum 2016.

[12] Zen is a clean sheet design that differs from AMD's previous long-standing Bulldozer architecture.

Zen-based processors use a 14 nm FinFET process, are reportedly more energy efficient, and can execute significantly more instructions per cycle.

[16] This SoC design allows the Zen microarchitecture to scale from laptops and small-form factor mini PCs to high-end desktops and servers.

[41] The "Summit Ridge" Zen family of CPUs use the AM4 socket and feature DDR4 support and a 95 W TDP (thermal design power).

[42] Each Zen core can decode four instructions per clock cycle and includes a micro-op cache which feeds two schedulers, one each for the integer and floating point segments.

AMD began planning the Zen microarchitecture shortly after re-hiring Jim Keller in August 2012.

[52] In November 2015, a source inside AMD reported that Zen microprocessors had been tested and "met all expectations" with "no significant bottlenecks found".

[54] This was clarified by AMD's July 2016 announcement that products had been successfully produced on Samsung's 14 nm FinFET process.

[58] Prior to Zen, AMD's smallest process size was 28 nm, as utilized by their Steamroller and Excavator microarchitectures.

[65] One of Zen's major goals in 2016 was to focus on performance per-core, and it was targeting a 40% improvement in instructions per cycle (IPC) over its predecessor.

[74] Pre-release reports stated APUs using the Zen architecture would also support High Bandwidth Memory (HBM).

The memory encryption mask (as well as other related information) is determined from settings returned through the same CPUID function that identifies the presence of the feature.

The memory controller contains a high-performance encryption engine which can be programmed with multiple keys for use by different VMs in the system.

The programming and management of these keys is handled by the AMD Secure Processor firmware which exposes an API for these tasks.

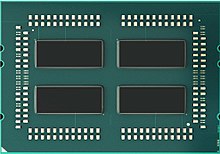

[80] Incorporating much of the southbridge into the SoC, the Zen CPU includes SATA, USB, and PCI Express NVMe links.

[83] AMD, in announcing its Radeon Instinct line, argued that the upcoming Zen-based Naples server CPU would be particularly suited for building deep learning systems.

[75][unreliable source][87][88] The first desktop processors without graphics processing units (codenamed "Summit Ridge") were initially expected to start selling at the end of 2016, according to an AMD roadmap; with the first mobile and desktop processors of the AMD Accelerated Processing Unit type (codenamed "Raven Ridge") following in late 2017.

The final clock speeds and TDPs for the 3 CPUs released in Q1 of 2017 demonstrated significant performance-per-watt benefits over the previous K15h (Piledriver) architecture.

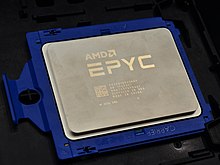

AMD announced in March 2017 that it would release a server platform based on Zen, codenamed Naples, in the second quarter of the year.

[121] On June 20, 2017, AMD officially released the Epyc 7000 series CPUs at a launch event in Austin, Texas.