Epyc

In March 2017, AMD announced plans to re-enter the server market with a platform based on the Zen microarchitecture, codenamed Naples, and officially revealed it under the brand name Epyc in May.

[3] In August 2019, the Epyc 7002 "Rome" series processors, based on the Zen 2 microarchitecture, launched, doubling the core count per socket to 64, and increasing per-core performance dramatically over the last generation architecture.

[6] In September 2021, Oak Ridge National Laboratory partnered with AMD and HPE Cray to build Frontier, a supercomputer with 9,472 Epyc 7453 CPUs and 37,888 Instinct MI250X GPUs, becoming operational by May 2022.

Codenamed Genoa, these CPUs are based on the Zen 4 microarchitecture and built on TSMC's N5 node, supporting up to 96 cores and 192 threads per socket, alongside 12 channels of DDR5[7] and 128 PCIe 5.0 lanes.

Genoa also became the first x86 server CPU to support Compute Express Link 1.1,[8] or CXL, allowing for further expansion of memory and other devices with a high bandwidth interface built on PCIe 5.0.

Bergamo is based on a modified version of Zen 4 named Zen 4c, designed to allow for much higher core counts and efficiency at the cost of lower single-core performance, targeting cloud providers and workloads, compared to traditional high performance computing workloads.

High memory bandwidth and extensive PCIe connectivity removed many bottlenecks, allowing all 96 cores to be utilized in workloads where previous generation Milan chips would have been I/O-bound.

Siena utilizes the same Zen 4c core architecture as Bergamo cloud native processors, allowing up to 64 cores per processor, and the same 6 nm I/O die as Bergamo and Genoa, although certain features have been cut down, such as reducing the memory support from 12 channels of DDR5 to only 6, and removing dual socket support.

Sharing the same SP5 socket as Genoa and Bergamo, Turin came with numerous platform advancements, including the support for up to 6400 MT/s DDR5 memory.

[16] AMD Epyc CPU codenames follow the naming scheme of Italian cities, including Milan, Rome, Naples, Genoa, Bergamo, Siena, Turin and Venice.

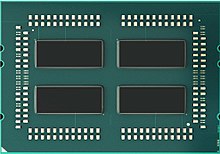

Epyc CPUs use a multi-chip module design to enable higher yields for a CPU than traditional monolithic dies.

In a dual socket configuration, 64 PCIe lanes from each CPU are allocated to AMD's proprietary Infinity Fabric interconnect to allow for full bandwidth between both CPUs.

That means most features required to make servers fully functional (such as memory, PCI Express, SATA controllers, etc.)

[27] Epyc was generally found to outperform Intel CPUs in cases where the cores could work independently, such as in high-performance computing and big-data applications.

First generation Epyc fell behind in database tasks compared to Intel's Xeon parts due to higher cache latency.

[44] Common features: At the HPC-AI Advisory Council in the United Kingdom in October 2019, AMD stated specifications for Milan, Epyc chips based on the Zen 3 microarchitecture.

[46] It also announced plans for the subsequent generation of chips, codenamed Genoa, that will be based on the Zen 4 microarchitecture and use Socket SP5.

[48][49][50] Common features: On November 10, 2022, AMD launched the fourth generation of Epyc server and data center processors based on the Zen 4 microarchitecture, codenamed Genoa.

[56] On September 18, 2023, AMD introduced the low power Siena lineup of processors, based on the Zen 4c microarchitecture.