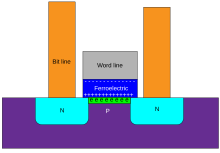

Fe FET

[1] Use of a ferroelectric (triglycine sulfate) in a solid state memory was proposed by Moll and Tarui in 1963 using a thin film transistor.

[2] Further research occurred in the 1960s, but the retention characteristics of the thin film based devices was unsatisfactory.

[3] Early field effect transistor based devices used bismuth titanate (Bi4Ti3O12) ferroelectric, or Pb1−xLnxTiO3 (PLT) and related mixed zirconate/titanates (PLZT).

Other challenges to feature shrinks include : reduced film thickness causing additional (undesired) polarisation effects; charge injection; and leakage currents.

[5] In 2017 FeFET based non-volatile memory was reported as having been built at 22nm node using FDSOI CMOS (fully depleted silicon on insulator) with hafnium dioxide (HfO2) as the ferroelectric- the smallest FeFET cell size reported was 0.025 μm2, the devices were built as 32Mbit arrays, using set/reset pulses of ~10ns duration at 4.2V - the devices showed endurance of 105 cycles and data retention up to 300C.