UltraRAM

[3] The Lancaster University researchers say that further work is ongoing to improve quality, fine-tune the fabrication process, and implement and scale UltraRAM devices.

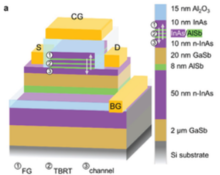

The presence of electrons in the FG (defining a logic 0 state) depletes carriers in the underlying n-type InAs channel, reducing its conductance.

This allows electrons to move rapidly across the TBRT region in the intended direction by the inherently fast quantum-mechanical process of resonant tunneling.

ULTRARAM prototype devices grown on GaAs substrates have previously exhibited experiment-limited, not device-limited, nonvolatile retention of 105 s and an endurance of 106 program-erase cycles.

[6] Consequently, due to the threshold voltage window of 350 mV in the devices designed by the Lancaster team, one can expect the 0/1 current contrast of ULTRARAM to improve to three decades with the implementation of a normally-off channel.

Professor Manus Hayne of the Department of Physics at Lancaster, who leads the work said, "ULTRARAM on silicon is a huge advance for our research, overcoming very significant materials challenges of large crystalline lattice mismatch, the change from elemental to compound semiconductor and differences in thermal contraction.