High Precision Event Timer

Compared to older types of timers available in the x86 architecture, HPET allows more efficient processing of highly timing-sensitive applications, such as multimedia playback and OS task switching.

Windows XP, when fitted with the latest hardware abstraction layer (HAL), can also use the processor's Time Stamp Counter (TSC), or ACPI Power Management Timer (ACPI PMTIMER), together with the RTC to provide operating system features that would, in later Windows versions, be provided by the HPET hardware.

The HPET can produce periodic interrupts at a much higher resolution than the RTC and is often used to synchronize multimedia streams, providing smooth playback and reducing the need to use other timestamp calculations such as an x86-based CPU's RDTSC instruction.

This provides improved efficiency, since the CPU does not need to waste cycles to make up for the low resolution of timers, and enables more aggressive use of sleep states, reducing power consumption.

Compared to these older timer circuits, the HPET has higher frequency and wider 64-bit counters (although they can be driven in 32-bit mode).

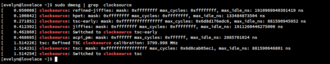

The documentation of Red Hat MRG version 2 states that TSC is the preferred clock source due to its much lower overhead, but it uses HPET as a fallback.

[6] In 2019 it was decided to blacklist HPET in newer Linux kernels when running on some Intel CPUs (Coffee Lake) because of its instability.

[8] Besides mentioning the race condition discussed above, a VMware document also lists some other drawbacks: "The specification does not require the timer to be particularly fine grained, to have low drift, or to be fast to read.

Some typical implementations run the counter at about 18 MHz and require about the same amount of time (1–2 μs) to read the HPET as with the ACPI timer.