Intel 8253

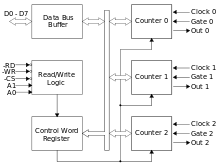

The Intel 8253 and 8254 are programmable interval timers (PITs), which perform timing and counting functions using three 16-bit counters.

In PC compatibles, Timer Channel 0 is assigned to IRQ-0 (the highest priority hardware interrupt).

The Intel 82c54 (c for CMOS logic) variant handles up to 10 MHz clock signals.

[3] The Read Back command being a vital I/O feature for interoperability with multicore CPUs and GPUs.

There is military version of Intel M8253 with the temperature range of -55 °C to +125 °C which it also have ±10% 5V power tolerance.

To initialize the counters, the microprocessor must write a control word (CW) in this register.

The counting process will start after the PIT has received these messages, and, in some cases, if it detects the rising edge from the GATE input signal.

After writing the Control Word and initial count, the Counter is armed.

An initial count of N will result in a one-shot pulse N CLK cycles in duration.

In this mode, the device acts as a divide-by-n counter, which is commonly used to generate a real-time clock interrupt.

is the number loaded into the counter (the COUNT message), the output will be high for

After Control Word and COUNT is loaded, the output will remain high until the counter reaches zero.

The counter will then generate a low pulse for 1 clock cycle (a strobe) – after that the output will become high again.

After receiving the Control Word and COUNT, the output will be set high.

Once the device detects a rising edge on the GATE input, it will start counting.

[9] In modern times, this PIT is not included as a separate chip in an x86 PC.

In a modern chipset, this change may show up in the form of noticeably faster access to the PIT's registers in the x86 I/O address space.

This is a holdover of the very first CGA PCs – they derived all necessary frequencies from a single quartz crystal, and to make TV output possible, this oscillator had to run at a multiple of the NTSC color subcarrier frequency.

This frequency, divided by 216 (the largest divisor the 8253 is capable of) produces the ≈18.2 Hz timer interrupt used in MS-DOS and related operating systems.

Newer motherboards include additional counters through the Advanced Configuration and Power Interface (ACPI), a counter on the Local Advanced Programmable Interrupt Controller, and a High Precision Event Timer.

Reprogramming typically happens during video mode changes, when the video BIOS may be executed, and during system management mode and power saving state changes, when the system BIOS may be executed.

The counter counts down to zero, then sends a hardware interrupt (IRQ 0, INT 8) to the CPU.

The slowest possible frequency, which is also the one normally used by computers running MS-DOS or compatible operating systems, is about 18.2 Hz.

However, in free-running counter applications such as in the x86 PC, it is necessary to first write a latch command for the desired channel to the control register, so that both bytes read will belong to one and the same value.

According to a 2002 Microsoft document, "because reads from and writes to this hardware [8254] require communication through an IO port, programming it takes several cycles, which is prohibitively expensive for the OS.