IBM RS64

IBM president Jack Kuehler wanted them to use PowerPC, but they resisted, arguing that the existing 32/64-bit PowerPC instruction set would not enable a viable transition for OS/400 software and that the existing instruction set required extensions for the commercial applications on the AS/400.

At Kuehler's insistence, a team at Rochester led by Frank Soltis investigated the feasibility of extending the PowerPC instruction set to support the needs of the AS/400 platform.

PowerPC processors developed in the AIM alliance suited the low-end RISC workstation and small server space well.

But mainframe and large clustered supercomputing systems required more performance and reliability, availability and serviceability features than processors designed for Apple Power Macs.

The Bellatrix project was extremely ambitious in its pervasive use of self-timed & pulse-based circuits and the EDA tools required to support this design strategy, and was eventually terminated.

To address technical workstation, supercomputer, and engineering/scientific markets, IBM Austin (the home of the RS/6000s) then started developing a time-to-market single-chip version of the Power2 (P2SC) in parallel with the development of a sophisticated 64-bit PowerPC processor with the POWER2 extensions and twin sophisticated MAF floating-point units (the POWER3/630).

To address RS/6000 commercial applications and AS/400 systems, IBM Rochester (the home of the AS/400s) started developing the first of the high-end 64-bit PowerPC processors with AS/400 extensions, and IBM Endicott started developing a low-end single-chip PowerPC processor with AS/400 extensions.

It was developed from "Cobra" and "Muskie" but included a more complete PowerPC ISA and was therefore set to be used in RS/6000 machines as well as in AS/400 systems.

It featured 128 KB total on-die L1 cache, 4 MB full speed off-chip L2 on a 128-bit bus, and a clock of 125 MHz.

Essentially, each chip stores state information for 2 threads at any given time and appears to be two processors to the OS.

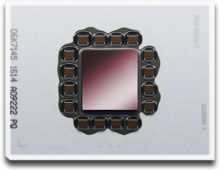

The RS64-III has 34 million transistors, a die size of 140 mm², and is manufactured on the 0.22 μm CMOS 7S process with six levels of copper interconnect.

In 2000, IBM launched a refined version called IStar manufactured with a SOI fabrication process with copper interconnects, which increased the processor's clock frequency to 600 MHz.

The integer / commercial workload performance of the RS-64 IV was similar to the Sun Microsystems processors with which it competed, though its floating point power was not comparable to the contemporary POWER3-II, which remained reasonably competitive throughout its lifecycle.