Integrating ADC

Their use is typically limited to digital voltmeters and other instruments requiring highly accurate measurements.

, the unknown input voltage: From the equation, one of the benefits of the dual-slope integrating ADC becomes apparent: the measurement is independent of the values of the circuit elements (R and C).

The required resolution (in number of bits) dictates the minimum length of the run-down period for a full-scale input (e.g.

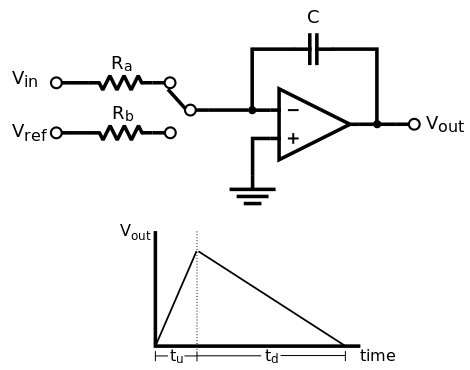

): During the measurement of a full-scale input, the slope of the integrator's output will be the same during the run-up and run-down phases.

Therefore, the total measurement time for a full-scale input will be based on the desired resolution and the frequency of the controller's clock: Typically the run-up time is chosen to be a multiple of the period of the mains frequency, to suppress mains hum.

It is not possible to increase the resolution of the basic dual-slope ADC to arbitrarily high values by using longer measurement times or faster clocks.

The run-up phase of the basic dual-slope design integrates the input voltage for a fixed period of time.

For a full-scale input equal to the reference voltage, half of the measurement time is spent in the run-up phase.

Using the same algorithm for the run-down phase results in the following equation for the calculation of the unknown input voltage (

One method to improve the resolution of the converter is to artificially increase the range of the integrating amplifier during the run-up phase.

Positive and negative reference voltages controlled by the two independent switches add and subtract charge as needed to keep the output of the integrator within its limits.

The controller keeps track of how often each switch is turned on in order to account for the additional charge placed onto (or removed from) the integrator capacitor as a result of the reference voltages.

The charge added / subtracted during the multi-slope run-up form the coarse part of the result (e.g. the leading 3 digits).

Each dashed vertical line represents a decision point by the controller where it samples the polarity of the output and chooses to apply either the positive or negative reference voltage to the input.

Ideally, the output voltage of the integrator at the end of the run-up period can be represented by the following equation: where

By using 4 slope rates that are each a power of ten more gradual than the previous, four digit resolution can be achieved in roughly 40 clock ticks—a huge speed improvement.

At the start of the run-down interval, the unknown input is removed from the circuit by opening the switch connected to

The combination of the run-down times for each of the slopes determines the value of the unknown input.

As explained below, the choice of the base affects the speed of the converter and determines the number of slopes needed to achieve the desired resolution.

The basis of this design is the assumption that there will always be overshoot when trying to find the zero crossing at the end of a run-down interval.

The time for the first-run down (using the steepest slope) is dependent on the unknown input (i.e., the amount of charge placed on the integrator capacitor during the run-up phase).

Since the equation depends on nearly all of the circuit's parameters, any variances in reference currents, the integrator capacitor, or other values will introduce errors in the result.

term to account for measured errors (or, as described in the referenced patent, to convert the residue ADC's output into the units of the run-up counters).

There is a certain amount of error involved in detecting the zero crossing using a comparator (one of the short-comings of the basic dual-slope design as explained above).

As the slope of the integrator voltage is constant during the run-down phase, the two voltage measurements can be used as inputs to an interpolation function that more accurately determines the time of the zero-crossing (i.e., with a much higher resolution than the controller's clock alone would allow).

By combining some of these enhancements to the basic dual-slope design (namely multi-slope run-up and the residue ADC), it is possible to construct an integrating analog-to-digital converter that is capable of operating continuously without the need for a run-down interval.

To start a conversion, two things happen simultaneously: the residue ADC is used to measure the approximate charge currently on the integrator capacitor and the counters monitoring the multi-slope run-up are reset.

At the end of a conversion period, another residue ADC reading is taken and the values of the multi-slope run-up counters are noted.

The unknown input is calculated using a similar equation as used for the residue ADC, except that two output voltages are included (

Another type of calibration requires external inputs of known quantities (e.g., voltage standards or precision resistance references) and would typically be performed infrequently (every year for equipment used in normal conditions, more often when being used in metrology applications).