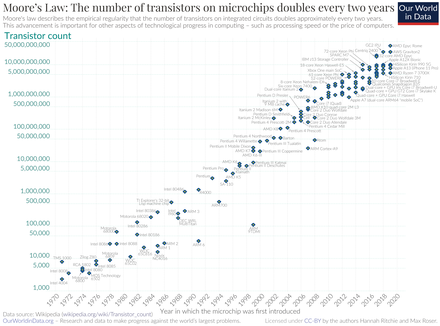

Moore's law

The observation is named after Gordon Moore, the co-founder of Fairchild Semiconductor and Intel and former CEO of the latter, who in 1965 noted that the number of components per integrated circuit had been doubling every year,[a] and projected this rate of growth would continue for at least another decade.

Moore's prediction has been used in the semiconductor industry to guide long-term planning and to set targets for research and development, thus functioning to some extent as a self-fulfilling prophecy.

Microprocessor architects report that semiconductor advancement has slowed industry-wide since around 2010, slightly below the pace predicted by Moore's law.

[3] In 1959, Douglas Engelbart studied the projected downscaling of integrated circuit (IC) size, publishing his results in the article "Microelectronics, and the Art of Similitude".

[19][20][21] He outlined several contributing factors for this exponential behavior:[12][13] Shortly after 1975, Caltech professor Carver Mead popularized the term Moore's law.

[25][26] The doubling period is often misquoted as 18 months because of a separate prediction by Moore's colleague, Intel executive David House.

[30] As a consequence of shrinking dimensions, Dennard scaling predicted that power consumption per unit area would remain constant.

[17] Koomey later showed that a similar rate of efficiency improvement predated silicon chips and Moore's law, for technologies such as vacuum tubes.

[25][34][17] Nevertheless, leading semiconductor manufacturers TSMC and Samsung Electronics have claimed to keep pace with Moore's law[35][36][37][38][39][40] with 10, 7, and 5 nm nodes in mass production.

Some of the key innovations are listed below, as examples of breakthroughs that have advanced integrated circuit and semiconductor device fabrication technology, allowing transistor counts to grow by more than seven orders of magnitude in less than five decades.

Computer industry technology road maps predicted in 2001 that Moore's law would continue for several generations of semiconductor chips.

[104] Pat Gelsinger, Intel CEO, stated at the end of 2023 that "we're no longer in the golden era of Moore's Law, it's much, much harder now, so we're probably doubling effectively closer to every three years now, so we've definitely seen a slowing.

These include the spin state of electron spintronics, tunnel junctions, and advanced confinement of channel materials via nano-wire geometry.

Compared to their silicon and germanium counterparts, InGaAs transistors are more promising for future high-speed, low-power logic applications.

Because of intrinsic characteristics of III–V compound semiconductors, quantum well and tunnel effect transistors based on InGaAs have been proposed as alternatives to more traditional MOSFET designs.

The zigzag edges of the nanoribbons introduce localized energy states in the conduction and valence bands and thus a bandgap that enables switching when fabricated as a transistor.

[117] In April 2005, Gordon Moore stated in an interview that the projection cannot be sustained indefinitely: "It can't continue forever.

[120] IEEE began a road-mapping initiative in 2016, Rebooting Computing, named the International Roadmap for Devices and Systems (IRDS).

[123][120][124] Although Moore's Law will reach a physical limit, some forecasters are optimistic about the continuation of technological progress in a variety of other areas, including new chip architectures, quantum computing, and AI and machine learning.

In situations in which security and survivability of hardware or data are paramount, or in which resources are limited, rapid obsolescence often poses obstacles to smooth or continued operations.

[138] Several measures of digital technology are improving at exponential rates related to Moore's law, including the size, cost, density, and speed of components.

Combined with Moore's law, performance per watt would grow at roughly the same rate as transistor density, doubling every 1–2 years.

[15][142] The primary reason cited for the breakdown is that at small sizes, current leakage poses greater challenges, and also causes the chip to heat up, which creates a threat of thermal runaway and therefore, further increases energy costs.

[143][144] In another departure from Dennard scaling, Intel microprocessors adopted a non-planar tri-gate FinFET at 22 nm in 2012 that is faster and consumes less power than a conventional planar transistor.

[164] Pixels per dollar – Similarly, Barry Hendy of Kodak Australia has plotted pixels per dollar as a basic measure of value for a digital camera, demonstrating the historical linearity (on a log scale) of this market and the opportunity to predict the future trend of digital camera price, LCD and LED screens, and resolution.

In a 2008 article in InfoWorld, Randall C. Kennedy,[169] formerly of Intel, introduces this term using successive versions of Microsoft Office between the year 2000 and 2007 as his premise.

Library expansion – was calculated in 1945 by Fremont Rider to double in capacity every 16 years, if sufficient space were made available.

[170] He advocated replacing bulky, decaying printed works with miniaturized microform analog photographs, which could be duplicated on-demand for library patrons or other institutions.

[172] Carlson accurately predicted that the doubling time of DNA sequencing technologies (measured by cost and performance) would be at least as fast as Moore's law.

Swanson's law is the observation that the price of solar photovoltaic modules tends to drop 20 percent for every doubling of cumulative shipped volume.