Inverter (logic gate)

[1] As with all binary logic gates, other pairs of symbols — such as true and false, or high and low — may be used in lieu of one and zero.

[3] A bar or overline ( ‾ ) above a variable can denote negation (or inversion or complement) performed by a NOT gate.

However, because current flows through the resistor in one of the two states, the resistive-drain configuration is disadvantaged for power consumption and processing speed.

[5] Processing speed can also be improved due to the relatively low resistance compared to the NMOS-only or PMOS-only type devices.

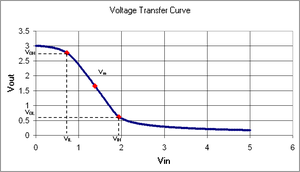

Digital electronics circuits operate at fixed voltage levels corresponding to a logical 0 or 1 (see binary).

An inverter circuit serves as the basic logic gate to swap between those two voltage levels.

From such a graph, device parameters including noise tolerance, gain, and operating logic levels can be obtained.

Ideally, the VTC appears as an inverted step function – this would indicate precise switching between on and off – but in real devices, a gradual transition region exists.

The tolerance to noise can be measured by comparing the minimum input to the maximum output for each region of operation (on / off).