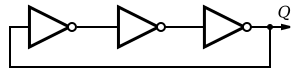

Ring oscillator

However, this configuration of inverter feedback can be used as a storage element and it is the basic building block of static random access memory or SRAM.

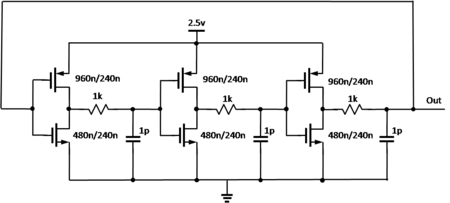

First, making the ring from a smaller number of inverters results in a higher frequency of oscillation, with about the same power consumption.

In circuits where this method can be applied, it reduces the propagation delay through the chain of stages, increasing both the frequency of the oscillation and the current consumed.

In a device fabricated with MOSFETs, for example, the gate capacitance must be charged before current can flow between the source and the drain.

From here, it can be easily seen that adding more inverters to the chain increases the total gate delay, reducing the frequency of oscillation.

Consider the initial case where the amplifier input and output voltages are momentarily balanced at a stable point.

The amplifier has a negative gain of greater than 1, so the output will change in the direction opposite to this input voltage.

The result of this sequential loop is a square-wave signal at the amplifier output with the period of each half of the square wave equal to the time delay.

Adding pairs of inverters to the ring increases the total delay and thereby decreases the oscillator frequency.