Transputer

Traditional complex instruction set computer (CISC) designs were reaching a performance plateau, and it wasn't clear it could be overcome.

A side effect of most multitasking design is that it often also allows the processes to be run on physically different CPUs, in which case it is termed multiprocessing.

In 1990, May received an Honorary DSc from University of Southampton, followed in 1991 by his election as a Fellow of The Royal Society and the award of the Patterson Medal of the Institute of Physics in 1992.

Tony Fuge, then a leading engineer at Inmos, was awarded the Prince Philip Designers Prize in 1987 for his work on the T414 transputer.

The goal was to produce a family of chips ranging in power and cost that could be wired together to form a complete parallel computer.

Inmos saw them being used for practically everything, from operating as the main CPU for a computer to acting as a channel controller for disk drives in the same machine.

It used microcode as the main method to control the data path, but unlike other designs of the time, many instructions took only one cycle to execute.

A hypothetical desktop machine might have two of the "low end" transputers handling input/output (I/O) tasks on some of their serial lines (hooked up to appropriate hardware) while they talked to one of their larger cousins acting as a CPU on another.

If BootFromROM was asserted when the chip was reset, it would begin processing at the instruction two bytes from the top of memory, which was normally used to perform a backward jump into the boot code.

The selected transputer would have the BootFromROM permanently asserted, which would cause it to begin running a booter process from ROM on startup.

The same logical system was used to communicate between programs running on one transputer, implemented as virtual network links in memory.

This allowed for very fast context switching by simply changing the workspace pointer to the memory used by another process (a method used in a number of contemporary designs, such as the TMS9900).

The lower nibble contained the one immediate constant operand, commonly used as an offset relative to the workspace (memory stack) pointer.

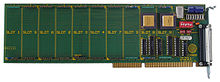

Inmos produced a range of TRAM motherboards for various host buses such as Industry Standard Architecture (ISA), MicroChannel, or VMEbus.

Unlike the earlier models, the T9000 had a true 16 KB high-speed cache (using random replacement) instead of RAM, but also allowed it to be used as memory and included MMU-like functionality to handle all of this (termed the PMI).

An interesting addition was the grouper[15] which would collect instructions out of the cache and group them into larger packages of up to 8 bytes to feed the pipeline faster.

By this time, the company had been sold to SGS-Thomson (now STMicroelectronics), whose focus was the embedded systems market, and eventually the T9000 project was abandoned.

The final design looked very similar to the original T4 core although some simple instruction grouping and a workspace cache were added to help with performance.

While the transputer was simple but powerful compared to many contemporary designs, it never came close to meeting its goal of being used universally in both CPU and microcontroller roles.

In the computer desktop and workstation field, the transputer was fairly fast (operating at about 10 million instructions per second (MIPS) at 20 MHz).

This was excellent performance for the early 1980s, but by the time the floating-point unit (FPU) equipped T800 was shipping, other RISC designs had surpassed it.

This could have been mitigated to a large extent if machines had used multiple transputers as planned, but T800s cost about $400 each when introduced, which meant a poor price/performance ratio.

Also, the Data Acquisition and Second Level Trigger systems of the High Energy Physics ZEUS Experiment for the Hadron Elektron Ring Anlage (HERA) collider at DESY was based on a network of over 300 synchronously clocked transputers divided into several subsystems.

The ability to quickly transform digital images in preparation for print gave the firm a significant edge over their competitors.

[citation needed] The German company Jäger Messtechnik used transputers for their early ADwin real-time data acquisition and control products.

The transputer also appeared in products related to virtual reality such as the ProVision 100 system made by Division Limited of Bristol, featuring a combination of Intel i860, 80486/33 and Toshiba HSP processors, together with T805 or T425 transputers, implementing a rendering engine that could then be accessed as a server by PC, Sun SPARCstation or VAX systems.

The combination of superscalar processing and speculative execution delivered a tangible performance increase on existing bodies of code – which were mostly written in Pascal, Fortran, C and C++.

Nevertheless, the model of cooperating concurrent processors can still be found in cluster computing systems that dominate supercomputer design in the 21st century.

Inevitably, microprocessor designers finally ran out of uses for the greater physical resources, almost at the same time when technology scaling began to hit its limits.

Some of the most powerful supercomputers in the world, based on designs from Columbia University and built as IBM Blue Gene, are real-world incarnations of the transputer dream.