7 nm process

In semiconductor manufacturing, the "7 nm" process is a term for the MOSFET technology node following the "10 nm" node, defined by the International Roadmap for Devices and Systems (IRDS), which was preceded by the International Technology Roadmap for Semiconductors (ITRS).

As of 2021, the IRDS Lithography standard gives a table of dimensions for the "7 nm" node,[1] with examples given below: The 2021 IRDS Lithography standard is a retrospective document, as the first volume production of a "7 nm" branded process was in 2016 with Taiwan Semiconductor Manufacturing Company's (TSMC) production of 256Mbit SRAM memory chips using a "7nm" process called N7.

"[4] Since at least 1997, the length scale of a process node has not referred to any particular dimension on the integrated circuits, such as gate length, metal pitch, or gate pitch, as new lithography processes no longer uniformly shrank all features on a chip.

By the late 2010s, the length scale had become a commercial name[5] that indicated a new generation of process technologies, without any relation to physical properties.

[6][7][8] Previous ITRS and IRDS standards had insufficient guidance on process node naming conventions to address the widely varying dimensions on a chip, leading to a divergence between how foundries branded their lithography and the actual dimensions their process nodes achieved.

[10] In 2019,[11] AMD released their "Rome" (EPYC 2) processors for servers and datacenters, which are based on TSMC's N7 node[12] and feature up to 64 cores and 128 threads.

[13][14] Shortly after, in 2003, NEC's researchers Hitoshi Wakabayashi and Shigeharu Yamagami advanced further by fabricating a 5nm MOSFET.

[2] In 2015, Intel expected that at the 7nm node, III-V semiconductors would have to be used in transistors, signaling a shift away from silicon.

[23] In April 2017, TSMC began risk production of 256Mbit SRAM memory chips using a "7nm" (N7FF+) process,[2] with extreme ultraviolet lithography (EUV).

[24] TSMC's "7nm" production plans, as of early 2017,[needs update] was to use deep ultraviolet (DUV) immersion lithography initially on this process node (N7FF), and transition from risk to commercial volume manufacturing from Q2 2017 to Q2 2018.

Also, their later generation "7nm" (N7FF+) production was planned[needs update] to use EUV multiple patterning and have an estimated transition from risk to volume manufacturing between 2018 and 2019.

[28] The company had not, at that time, published any expected values for feature lengths at this process node.

At their Q1 2019 earnings call, TSMC reiterated their Q4 2018 statement[31] that N7+ was at that time expected to have generated less than $1 billion TWD in revenue in 2019.

[35][needs update] On October 5, 2019, AMD announced their EPYC Roadmap, featuring Milan chips built using TSMC's N7+ process.

[36][needs update] On October 7, 2019, TSMC announced they had started delivering N7+ products to market in high volume.

[37][needs update] On July 26, 2021, Intel announced their new manufacturing roadmap, renaming all of their future process nodes.

[39][needs update] In June 2018, AMD announced 7nm Radeon Instinct GPUs launching in the second half of 2018.

[42][43] On October 30, 2018, Apple announced their A12X Bionic chip used in iPad Pro built using TSMC's 7nm (N7) process.

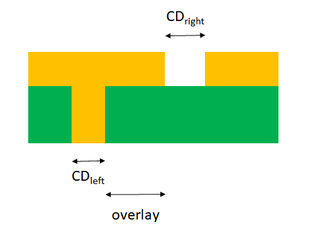

Each of these technologies carries significant challenges in critical dimension (CD) control as well as pattern placement, all involving neighboring features.

After removing the core features, the spacers are used as an etch mask to define trenches in the underlying layer.

This is actually expected to have less variation than pitch splitting, where an additional exposure defines its own CD, both directly and through overlay.

[59] EUV also has issues with reliably printing all features in a large population; some contacts may be completely missing or lines bridged.

[62] The tip-to-tip gap is hard to control for EUV, largely due to the illumination constraint.

Attenuated phase shift masks have been used in production for 90 nm node for adequate focus windows for arbitrarily pitched contacts with the ArF laser wavelength (193nm),[64][65] whereas this resolution enhancement is not available for EUV.

[68] Due to these challenges, "7nm" poses unprecedented patterning difficulty in the back end of line (BEOL).

[74] However, self-aligned quad patterning (SAQP) is used to form the fin, the most important factor to performance.