Charge trap flash

The same business, now operating under the Spansion name, has produced charge trapping devices in high volume since that time.

Saifun Semiconductors, who licensed a large charge trapping technology portfolio to several companies, was acquired by Spansion in March 2008.

From the late 2000s, CTF became a core component of 3D V-NAND flash memory developed by Toshiba and Samsung Electronics.

Chen of Fairchild Camera and Instrument published a paper[11] detailing the invention of SONOS, a MOSFET technology with far less demanding program and erase conditions and longer charge storage.

In 1991, Japanese NEC researchers including N. Kodama, K. Oyama and Hiroki Shirai developed a type of flash memory that incorporated a charge trap method.

[15] That year, AMD (in a division later spun off as Spansion) announced a new flash memory technology it called "MirrorBit".

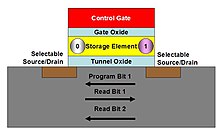

Shown in Figure 1 the bits reside at opposite ends of the cell and can be read by running a current through the channel in different directions.

Those electrons that have gained sufficient energy in traversing through the high-field region near the drain will boil off from the channel to be injected into the charge trapping layer where they come to rest.

Freescale Semiconductor manufactures a somewhat similar technology the company calls "Thin Film Storage" in its microcontroller or MCU line.

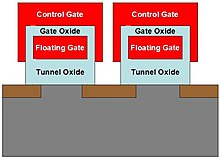

Like the more conventional silicon nitride charge trap, electrons do not flow from one side of the floating gate to the other, extending the cell's wear.

This nanocrystal approach is being manufactured in volume by Freescale and charge trapping storage in general is in development at ST Microelectronics, Philips, Renesas, Samsung, Toshiba, Atmel, and Spansion.

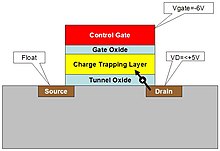

The technology depends on a SONOS (silicon–oxide–nitride–oxide–silicon) or MONOS (metal-ONOS) capacitor structure, storing the information in charge traps in the nitride layer.

Samsung disclosed two cell structures: TANOS (Titanium, Alumina, Nitride, Oxide, Silicon) for 40 nm, where researchers believed that the existing 3D cap structure (described in detail later in this article) could not be manufactured, and THNOS, in which the aluminum oxide would be replaced with an undisclosed high-k dielectric material.

Over the following five years many device designers found ways to push the cap structure to increasingly tighter process geometries, successfully producing NAND at the 30 nm node with this approach.

Charge trapping is still viewed as a future technology for NAND flash, but it is being considered more for vertical structures than for planar cells.

Samsung even announced[21] in late 2006 that by 2008 it would put such a device into production at the 40 nm process node, but over the five years following this announcement many device designers found ways to push the cap structure to increasingly tighter process geometries, successfully producing NAND down to 20 nm node with this approach.

The charge trapping approach is still viewed as a future for NAND flash for processes smaller than 20 nm and is being considered for both planar as well as vertical 3D structures.

[22] This implies that standard device structures could stay in place until the industry reaches 10 nm, however the challenges of producing a reliable floating gate become more severe with each process shrink.

The vertical structures (only one shown) are cylinders that implement a channel that is wrapped in alternating dielectric and charge trapping layers (blue and yellow).

One advantage that charge trapping flash has over other technologies is that it can be relatively easily embedded with a standard logic process.

[26] In ITRS PIDS 2013, it was clearly mentioned that bandgap engineered charge-trapping devices are needed to resolve the retention and erase dilemma.

In order to erase the device quickly holes in the substrate are injected into the SiN to neutralize the electron charge.

For example, triple ultra-thin (1–2 nm) layers of ONO are introduced to replace the single oxide (BE-SONOS) [H. T. Lue, et al, IEDM 2005].

Later BE-SONOS is added high-K (Al2O3) and metal gate to enhance the erase performances, the so-called BE-MANOS [S. C. Lai, et al, NVSMW 2007].

Right now the mass production 3D NAND adopts a similar structure of BE-MANOS, with some variations of detail recipe tuning by each individual companies.

Although charge trapping NAND can help the GCR and FG cross talk issues and thus promises scaling below 20nm it does not help the fundamental limitations such as word line breakdown and too few electrons.