Clock skew

Clock skew (sometimes called timing skew) is a phenomenon in synchronous digital circuit systems (such as computer systems) in which the same sourced clock signal arrives at different components at different times due to gate or, in more advanced semiconductor technology, wire signal propagation delay.

Ideally, the input to each memory element reaches its final value in time for the next clock tick so that the behavior of the whole circuit can be predicted exactly.

The maximum speed at which a system can run must account for the variance that occurs between the various elements of a circuit due to differences in physical composition, temperature, and path length.

This is called a hold violation because the previous data is not held long enough at the destination flip-flop to be properly clocked through.

If it fails to do so, a setup violation occurs, so-called because the new data was not set up and stable before the next clock tick arrived.

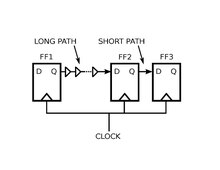

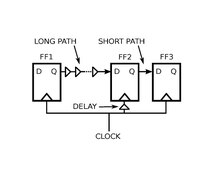

Figures 1 and 2 illustrate a situation where intentional clock skew can benefit a synchronous circuit.

A small amount of extra delay is interposed before FF2's clock input, which then safely positions the FF2 -> FF3 path away from its hold violation.

In addition, safety margins greater than or equal to the zero skew case can be guaranteed by setting setup and hold times and jitter bound appropriately in the linear program.

Thus, in the usual case of sending and receiving registers at different locations, there is no clear way to separate the total clock timing uncertainty into spatial skew and jitter.

[4] Network operations that require timestamps which are comparable across hosts can be affected by clock skew.

Some applications (such as game servers) may also use their own synchronization mechanism to avoid reliability problems due to clock skew.

Clock skew is the reason why at fast speeds or long distances, serial interfaces (e.g.