Magnetic-core memory

Depending on the direction of the currents, the core will pick up a clockwise or counterclockwise magnetic field, storing a 1 or 0.

Read-only core rope memory, for example, was used on the mission-critical Apollo Guidance Computer essential to NASA's successful Moon landings.

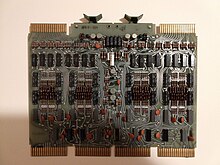

Reaching this density requires extremely careful manufacturing, which was almost always carried out by hand in spite of repeated major efforts to automate the process.

The files that result from saving the entire contents of memory to disk for inspection, which is nowadays commonly performed automatically when a major error occurs in a computer program, are still called "core dumps".

The basic concept of using the square hysteresis loop of certain magnetic materials as a storage or switching device was known from the earliest days of computer development.

Much of this knowledge had developed due to an understanding of transformers, which allowed amplification and switch-like performance when built using certain materials.

The stable switching behavior was well known in the electrical engineering field, and its application in computer systems was immediate.

For example, J. Presper Eckert and Jeffrey Chuan Chu had done some development work on the concept in 1945 at the Moore School during the ENIAC efforts.

[2] Robotics pioneer George Devol filed a patent[3] for the first static (non-moving) magnetic memory on 3 April 1946.

Substantial work in the field was carried out by the Shanghai-born American physicists An Wang and Way-Dong Woo, who created the pulse transfer controlling device in 1949.

A signal generator produced a series of pulses which were sent into the control transformers at half the energy needed to flip the polarity.

The MIT Project Whirlwind computer required a fast memory system for real-time aircraft tracking.

Several researchers in the late 1940s conceived the idea of using magnetic cores for computer memory, but MIT computer engineer Jay Forrester received the principal patent for his invention of the coincident-current core memory that enabled the 3D storage of information.

[12][13] William Papian of Project Whirlwind cited one of these efforts, Harvard's "Static Magnetic Delay Line", in an internal memo.

[15] Forrester has since observed, "It took us about seven years to convince the industry that random-access magnetic-core memory was the solution to a missing link in computer technology.

A prolific inventor, Rajchman designed a unique core system using ferrite bands wrapped around thin metal tubes,[17] building his first examples using a converted aspirin press in 1949.

This started a long series of lawsuits, which eventually ended when IBM bought the patent outright from Wang for US$500,000.

In 1964, after years of legal wrangling, IBM paid MIT $13 million for rights to Forrester's patent—the largest patent settlement to that date.

[28] Use of this machine reduced the time taken to thread the straight X and Y select lines from 25 hours to 12 minutes on a 128 by 128 core array.

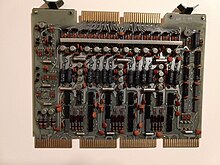

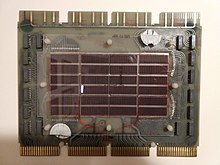

[40][41][42] In 1980, the price of a 16 kW (kiloword, equivalent to 32 kB) core memory board that fitted into a DEC Q-bus computer was around US$3,000.

Core relies on the square hysteresis loop properties of the ferrite material used to make the toroids.

To select a memory location, one of the X and one of the Y lines are driven with half the current ("half-select") required to cause this change.

This offered a performance advantage over X/Y line coincident-current in that multiple words could be cleared or written with the same value in a single cycle.

Some designs had substantially higher performance: the CDC 6600 had a memory cycle time of 1.0 μs in 1964, using cores that required a half-select current of 200 mA.

These were important advantages for some applications like first-generation industrial programmable controllers, military installations and vehicles like fighter aircraft, as well as spacecraft, and led to core being used for a number of years after availability of semiconductor MOS memory (see also MOSFET).

Diagnosing hardware problems in core memory required time-consuming diagnostic programs to be run.

As most computers had just a single core-memory board, these diagnostics also moved themselves around in memory, making it possible to test every bit.

The data plot of this test seemed to resemble a cartoon character called "Shmoo," and the name stuck.

In many occasions, errors could be resolved by gently tapping the printed circuit board with the core array on a table.

The procedure was seldom needed, as core memory proved to be very reliable compared to other computer components of the day.