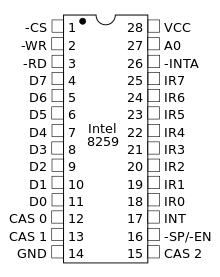

Intel 8259

The initial part was 8259, a later A suffix version was upward compatible and usable with the 8086 or 8088 processor.

The 8259 has coexisted with the Intel APIC Architecture since its introduction in symmetric multiprocessor PCs.

Modern PCs have begun to phase out the 8259A in favor of the Intel APIC Architecture.

However, while not anymore a separate chip, the 8259A interface is still provided by the Platform Controller Hub or southbridge on modern x86 motherboards.

Auto-EOI resets the IRQ level in the ISR immediately after the interrupt is acknowledged.

This prevents the use of any of the 8259's other EOI modes in DOS, and excludes the differentiation between device interrupts rerouted from the master 8259 to the slave 8259.

This was done despite the first 32 (INT00-INT1F) interrupt vectors being reserved by the processor for internal exceptions (this was ignored for the design of the PC for some reason).

This is especially important for modern x86 hardware in which a significant amount of time may be spent on I/O address space delay when communicating with the 8259s.

On newer EISA, PCI, and later systems the Edge/Level Control Registers (ELCRs) control the mode per IRQ line, effectively making the mode of the 8259 irrelevant for such systems with ISA buses.

In edge triggered mode, the noise must maintain the line in the low state for 100 ns.

When the noise diminishes, a pull-up resistor returns the IRQ line to high, thus generating a false interrupt.

A similar case can occur when the 8259 unmask and the IRQ input de-assertion are not properly synchronized.

The second is the master 8259's IRQ2 is active high when the slave 8259's IRQ lines are inactive on the falling edge of an interrupt acknowledgment.