MOS Technology 6502

Soon after the 6502's introduction, MOS Technology was purchased outright by Commodore International, who continued to sell the microprocessor and licenses to other manufacturers.

[16] In May 1972, Motorola's engineers began visiting select customers and sharing the details of their proposed 8-bit microprocessor system with ROM, RAM, parallel and serial interfaces.

They offered development software on a timeshare computer, the "EXORciser" debugging system, onsite training and field application engineer support.

[25] Motorola's Semiconductor Products Division management showed no interest in Peddle's low-cost microprocessor proposal.

[26] Peddle responded to the order by informing Motorola that the letter represented an official declaration of "project abandonment", and as such, the intellectual property he had developed to that point was now his.

The new group vice president John Welty said, "The semiconductor sales organization lost its sensitivity to customer needs and couldn't make speedy decisions.

[30] Paivinen then formed MOS Technology in Valley Forge, Pennsylvania in 1969 with two other executives from General Instrument, Mort Jaffe and Don McLaughlin.

[33] On 19 August 1974, Chuck Peddle, Bill Mensch, Rod Orgill, Harry Bawcom, Ray Hirt, Terry Holdt, and Wil Mathys left Motorola to join MOS.

The goal of the team was to design and produce a low-cost microprocessor for embedded applications and to target as wide as possible a customer base.

[34] Mensch later stated the goal was not the processor price itself, but to create a set of chips that could sell at $20 to compete with the recently introduced Intel 4040 that sold for $29 in a similar complete chipset.

[40] A further advantage was that depletion-load designs used less power while switching, thus running cooler and allowing higher operating speeds.

A September 1975 article in EDN magazine gives this summary of the design:[43] The MOS Technology 650X family represents a conscious attempt of eight former Motorola employees who worked on the development of the 6800 system to put out a part that would replace and outperform the 6800, yet undersell it.

The 6502 simply removed this feature, in keeping with its design as an inexpensive controller being used for specific tasks and communicating with simple devices.

General-purpose registers like accumulators have to be accessed by many parts of the instruction decoder, and thus require significant amounts of wiring to move data to and from their storage.

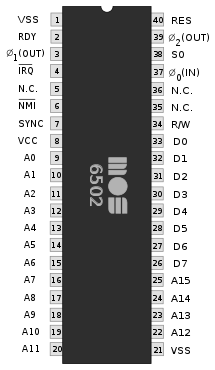

[48][b] MOS would introduce two microprocessors based on the same underlying design: the 6501 would plug into the same socket as the Motorola 6800, while the 6502 re-arranged the pinout to support an on-chip clock oscillator.

Chuck Peddle's goal was to sell the first run 6501 and 6502 chips to the attendees at the WESCON trade show in San Francisco beginning on September 16, 1975.

[60] On November 3, 1975, Motorola sought an injunction in Federal Court to stop MOS Technology from making and selling microprocessor products.

Four of the former Motorola engineers were named in the suit: Chuck Peddle, Will Mathys, Bill Mensch and Rod Orgill.

During the discovery process, Motorola found that one engineer, Mike Janes, had ignored Peddle's instructions and brought his 6800 design documents to MOS Technology.

Another group inside the company designed the KIM-1, which was sold semi-complete and could be turned into a usable system with the addition of a 3rd party computer terminal and compact cassette drive.

The 6510, a direct successor of the 6502 with a digital I/O port and a tri-state address bus, was the CPU utilized in the best-selling[68][69] Commodore 64 home computer.

The 6502 used in the NES was a second source version by Ricoh, a partial system on a chip, that lacked the binary-coded decimal mode but added 22 memory-mapped registers and on-die hardware for sound generation, joypad reading, and sprite list DMA.

The Atari Lynx used a custom chip named "Mikey"[71] designed by Epyx which included a VLSI VL65NC02 licensed cell.

Like most simple CPUs of the era, the dynamic NMOS 6502 chip is not sequenced by microcode but decoded directly using a dedicated PLA.

Software access to the stack is done via four implied addressing mode instructions, whose functions are to push or pop (pull) the accumulator or the processor status register.

With the 5/6 cycle "(indirect),y" mode, the 8-bit Y register is added to a 16-bit base address read from zero page, which is located by a single byte following the opcode.

[78] This pattern is not universal, as there are exceptions, but it allows opcode values to be easily converted to assembly mnemonics for the majority of instructions, handling the edge cases with special-purpose code.

The 65C816, the 16-bit CMOS descendant of the 6502, also supports 24-bit addressing, which results in instructions being assembled with three-byte operands, also arranged in little-endian format.

The W65C816S is a newer variant of the 65C816, which is the core of the Apple IIGS computer and is the basis of the Ricoh 5A22 processor that powers the Super Nintendo Entertainment System.

Among these improvements was conversion to a static core, which makes it possible to stop the clock in either phase without the registers losing data.