Phase-locked loop

Since 1969, a single integrated circuit can provide a complete PLL building block, and nowadays have output frequencies from a fraction of a hertz up to many gigahertz.

Thus, PLLs are widely employed in radio, telecommunications, computers (e.g. to distribute precisely timed clock signals in microprocessors), grid-tie inverters (electronic power converters used to integrate DC renewable resources and storage elements such as photovoltaics and batteries with the power grid), and other electronic applications.

A simple analog PLL is an electronic circuit consisting of a variable frequency oscillator and a phase detector in a feedback loop (Figure 1).

Spontaneous synchronization of weakly coupled pendulum clocks was noted by the Dutch physicist Christiaan Huygens as early as 1673.

[1] Around the turn of the 19th century, Lord Rayleigh observed synchronization of weakly coupled organ pipes and tuning forks.

[4] In 1925, David Robertson, first professor of electrical engineering at the University of Bristol, introduced phase locking in his clock design to control the striking of the bell Great George in the new Wills Memorial Building.

The technique was described in 1932, in a paper by Henri de Bellescize, in the French journal L'Onde Électrique.

[5][6][7] In analog television receivers since at least the late 1930s, phase-locked-loop horizontal and vertical sweep circuits are locked to synchronization pulses in the broadcast signal.

[8] In 1969, Signetics introduced a line of low-cost monolithic integrated circuits like the NE565 using bipolar transistors, that were complete phase-locked loop systems on a chip,[9] and applications for the technique multiplied.

A few years later, RCA introduced the CD4046 Micropower Phase-Locked Loop using CMOS, which also became a popular integrated circuit building block.

The receiver generates a clock from an approximate frequency reference, and then uses a PLL to phase-align it to the data stream's signal edges.

[14] Many electronic systems include processors of various sorts that operate at hundreds of megahertz to gigahertz, well above the practical frequencies of crystal oscillators.

Various regulatory agencies (such as the FCC in the United States) put limits on the emitted energy and any interference caused by it.

The emitted noise generally appears at sharp spectral peaks (usually at the operating frequency of the device, and a few harmonics).

A system designer can use a spread-spectrum PLL to reduce interference with high-Q receivers by spreading the energy over a larger portion of the spectrum.

For example, by changing the operating frequency up and down by a small amount (about 1%), a device running at hundreds of megahertz can spread its interference evenly over a few megahertz of spectrum, which drastically reduces the amount of noise seen on broadcast FM radio channels, which have a bandwidth of several tens of kilohertz.

The best digital PLLs are constructed with emitter-coupled logic (ECL) elements, at the expense of high power consumption.

To further improve the phase noise of the output, an injection locked oscillator can be employed following the VCO in the PLL.

GSM local oscillator modules are typically built with a frequency synthesizer integrated circuit and discrete resonator VCOs.

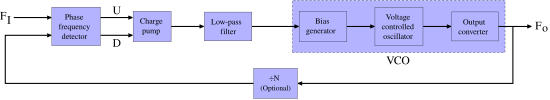

[citation needed] The block diagram shown in the figure shows an input signal, FI, which is used to generate an output, FO.

The output is fed through an optional divider back to the input of the system, producing a negative feedback loop.

The PD output voltage is used to control the VCO such that the phase difference between the two inputs is held constant, making it a negative feedback system.

For instance, the frequency mixer produces harmonics that adds complexity in applications where spectral purity of the VCO signal is important.

In these applications the more complex digital phase detectors are used which do not have as severe a reference spur component on their output.

The second common consideration is limiting the amount of reference frequency energy (ripple) appearing at the phase detector output that is then applied to the VCO control input.

[citation needed] PLLs may include a divider between the oscillator and the feedback input to the phase detector to produce a frequency synthesizer.

A programmable divider is particularly useful in radio transmitter applications and for computer clocking, since a large number of frequencies can be produced from a single stable, accurate, quartz crystal–controlled reference oscillator (which were expensive before commercial-scale hydrothermal synthesis provided cheap synthetic quartz).

The equations governing a phase-locked loop with an analog multiplier as the phase detector and linear filter may be derived as follows.

The time-domain model takes the form PD characteristics for this signals is equal[21] to Hence the phase domain model takes the form This system of equations is equivalent to the equation of mathematical pendulum Phase locked loops can also be analyzed as control systems by applying the Laplace transform.

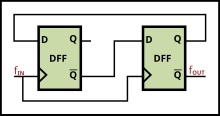

(See the D Banerjee ref below) Digital phase locked loops can be implemented in hardware, using integrated circuits such as a CMOS 4046.