Physical design (electronics)

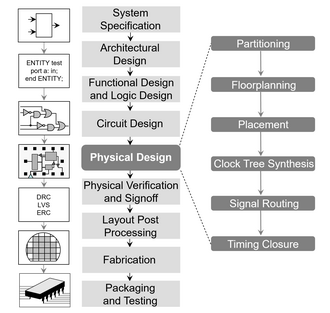

This step is usually split into several sub-steps, which include both design and verification and validation of the layout.

[3] This is followed by the Fabrication or Manufacturing Process where designs are transferred onto silicon dies which are then packaged into ICs.

The physical design flow uses the technology libraries that are provided by the fabrication houses.

These technology files provide information regarding the type of silicon wafer used, the standard-cells used, the layout rules (like DRC in VLSI), etc.

The reason being that one has the flexibility to design/modify design blocks from vendor provided libraries in ASIC.

Physical design is based on a netlist which is the end result of the synthesis process.

Synthesis converts the RTL design usually coded in VHDL or Verilog HDL to gate-level descriptions which the next set of tools can read/understand.

This is done mainly to separate different functional blocks and also to make placement and routing easier.

Floorplanning is the process of identifying structures that should be placed close together, and allocating space for them in such a manner as to meet the sometimes conflicting goals of available space (cost of the chip), required performance, and the desire to have everything close to everything else.

A bad floorplan will lead to wastage of die area and routing congestion.

Example structures that make up data paths are Adders, Subtractors, Counters, Registers, and Muxes.

Before the start of placement optimization all Wire Load Models (WLM) are removed.

Placement uses RC values from Virtual Route (VR) to calculate timing.

Placement is performed in four optimization phases: The goal of clock tree synthesis (CTS) is to minimize skew and insertion delay.

It converts the physical layout (polygons) into mask data (instructions for the photomask writer).