Wafer (electronics)

It undergoes many microfabrication processes, such as doping, ion implantation, etching, thin-film deposition of various materials, and photolithographic patterning.

The round shape characteristic of these wafers comes from single-crystal ingots usually produced using the Czochralski method.

In 1965, American engineers Eric O. Ernst, Donald J. Hurd, and Gerard Seeley, while working under IBM, filed Patent US3423629A[4] for the first high-capacity epitaxial apparatus.

Silicon wafers are made by companies such as Sumco, Shin-Etsu Chemical,[5] Hemlock Semiconductor Corporation and Siltronic.

Wafers are formed of highly pure,[6] nearly defect-free single crystalline material, with a purity of 99.9999999% (9N) or higher.

In this process, a cylindrical ingot of high purity monocrystalline semiconductor, such as silicon or germanium, called a boule, is formed by pulling a seed crystal from a melt.

[7][8] Donor impurity atoms, such as boron or phosphorus in the case of silicon, can be added to the molten intrinsic material in precise amounts in order to dope the crystal, thus changing it into an extrinsic semiconductor of n-type or p-type.

[13][14] Semiconductor fabrication plants, colloquially known as fabs, are defined by the diameter of wafers that they are tooled to produce.

[21] Meanwhile world's first Silicon Carbide (SiC) 200 mm wafers were announced in July 2021 by ST Microelectronics.

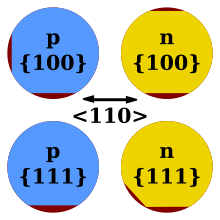

Ion implantation depths depend on the wafer's crystal orientation, since each direction offers distinct paths for transport.

In earlier-generation wafers a pair of flats at different angles additionally conveyed the doping type (see illustration for conventions).

[citation needed] There are also issues related to increased inter-die / edge-to-edge wafer variation and additional edge defects.

[32][33] In November 2013 ASML paused development of 450-mm lithography equipment, citing uncertain timing of chipmaker demand.

[34] In 2012, a group consisting of New York State (SUNY Poly/College of Nanoscale Science and Engineering (CNSE)), Intel, TSMC, Samsung, IBM, Globalfoundries and Nikon companies has formed a public-private partnership called Global 450mm Consortium (G450C, similar to SEMATECH) who made a 5-year plan (expiring in 2016) to develop a "cost effective wafer fabrication infrastructure, equipment prototypes and tools to enable coordinated industry transition to 450mm wafer level".

[38][39][40] Various sources have speculated that demise of the group came after charges of bid rigging made against Alain E. Kaloyeros, who at the time was a chief executive at the SUNY Poly.

[40][39][41] The industry realization of the fact that the 300mm manufacturing optimization is more cheap than costly 450mm transition may also have played a role.

[42][43] Mark Durcan, then CEO of Micron Technology, said in February 2014 that he expects 450 mm adoption to be delayed indefinitely or discontinued.

According to this report some observers expected 2018 to 2020, while G. Dan Hutcheson, chief executive of VLSI Research, didn't see 450mm fabs moving into production until 2020 to 2025.

These major investments were undertaken in the economic downturn following the dot-com bubble, resulting in huge resistance to upgrading to 450 mm by the original timeframe.

[citation needed] All told, the development of 450 mm wafers requires significant engineering, time, and cost to overcome.

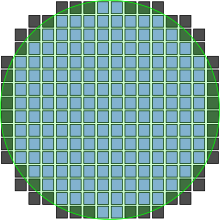

In general, this is a computationally complex problem with no analytical solution, dependent on both the area of the dies as well as their aspect ratio (square or rectangular) and other considerations such as the width of the scribeline or saw lane, and additional space occupied by alignment and test structures.

It will always overestimate the true best-case gross DPW, since it includes the area of partially patterned dies which do not fully lie on the wafer surface (see figure).

In the other limiting case (infinitesimally small dies or infinitely large wafers), the edge correction is negligible.