ARM Cortex-M

These cores are optimized for low-cost and energy-efficient integrated circuits, which have been embedded in tens of billions of consumer devices.

ARM Limited neither manufactures nor sells CPU devices based on its own designs, but rather licenses the processor architecture to interested parties.

Integrated Device Manufacturers (IDM) receive the ARM Processor IP as synthesizable RTL (written in Verilog).

This allows the manufacturer to achieve custom design goals, such as higher clock speed, very low power consumption, instruction set extensions (including floating point), optimizations for size, debug support, etc.

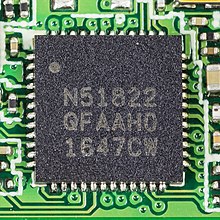

To determine which components have been included in a particular ARM CPU chip, consult the manufacturer datasheet and related documentation.

All Cortex-M cores implement a common subset of instructions that consists of most Thumb-1, some Thumb-2, including a 32-bit result multiply.

The Cortex-M0 / M0+ / M1 include a minor subset of Thumb-2 instructions (BL, DMB, DSB, ISB, MRS, MSR).

The Cortex-M0+ pipeline was reduced from 3 to 2 stages, which lowers the power usage and increases performance (higher average IPC due to branches taking one fewer cycle).

The Cortex-M0+ also received Cortex-M3 and Cortex-M4 features, which can be added as silicon options, such as the memory protection unit (MPU) and the vector table relocation.

[32] On 21 June 2018, the "world's smallest computer'", or computer device was announced – based on the ARM Cortex-M0+ (and including RAM and wireless transmitters and receivers based on photovoltaics) – by University of Michigan researchers at the 2018 Symposia on VLSI Technology and Circuits with the paper "A 0.04mm3 16nW Wireless and Batteryless Sensor System with Integrated Cortex-M0+ Processor and Optical Communication for Cellular Temperature Measurement."

The device is one-tenth the size of IBM's previously claimed world-record-sized computer from months back in March 2018, which is smaller than a grain of salt.

It is conceptually a Cortex-M33 core with a new instruction cache, plus new tamper-resistant hardware concepts borrowed from the ARM SecurCore family, and configurable parity and ECC features.

[10] Currently, information about the Cortex-M35P is limited, because its Technical Reference Manual and Generic User Guide haven't been released yet.

24 MHz ARM Cortex-M3 microcontroller with 16 KB flash memory , 4 KB RAM. Manufactured by STMicroelectronics .