hyperSPARC

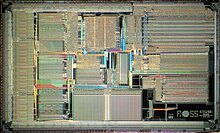

The hyperSPARC, code-named "Pinnacle", is a microprocessor that implements the SPARC Version 8 instruction set architecture (ISA) developed by Ross Technology for Cypress Semiconductor.

Integer multiply and divide, instructions added in the V8 version of the SPARC architecture, had an 18- and 37-cycle latency, respectively, and stalled the pipeline until they were completed.

It was fabricated by Cypress in their 0.65 μm, two-layer metal, complementary metal–oxide–semiconductor (CMOS) process.

It was packaged in a ceramic multi-chip module (MCM) with a pin grid array (PGA).

It was developed by Santa Clara, California start-up Nimbus Technologies, Inc. for Cypress, who fabricated the design.