Signal integrity

Over short distances and at low bit rates, a simple conductor can transmit this with sufficient fidelity.

At high bit rates and over longer distances or through various mediums, various effects can degrade the electrical signal to the point where errors occur and the system or device fails.

Such performance is a matter of basic physics and as such has remained relatively unchanged since the inception of electronic signaling.

In the early days of the modern VLSI era, digital chip circuit design and layout were manual processes.

However, scaling trends (see Moore's law) brought electrical effects back to the forefront in recent technology nodes.

In nanometer technologies at 0.13 μm and below, unintended interactions between signals (e.g. crosstalk) became an important consideration for digital design.

Therefore, electronic design automation (EDA) tools have been developed to analyze, prevent, and correct these problems.

The channel flight time (delay) of the interconnect is roughly 1 ns per 15 cm (6 in) of FR-4 stripline (the propagation velocity depends on the dielectric and the geometry).

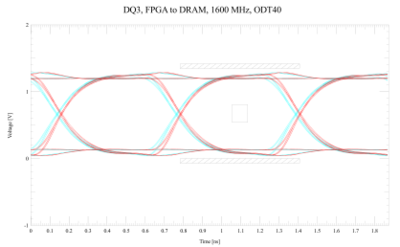

[5] Reflections of previous pulses at impedance mismatches die down after a few bounces up and down the line (i.e. on the order of the flight time).

The gentle trend to higher bit rates accelerated dramatically in 2004, with the introduction by Intel of the PCI-Express standard.

Following this lead, the majority of chip-to-chip connection standards underwent an architectural shift from parallel buses to serializer/deserializer (SERDES) links called "lanes."

At multigigabit/s data rates, link designers must consider reflections at impedance changes (e.g. where traces change levels at vias, see Transmission lines), noise induced by densely packed neighboring connections (crosstalk), and high-frequency attenuation caused by the skin effect in the metal trace and dielectric loss tangent.

Examples of mitigation techniques for these impairments are a redesign of the via geometry to ensure an impedance match, use of differential signaling, and preemphasis filtering, respectively.

As a consequence of the low impedance required by matching, PCB signal traces carry much more current than their on-chip counterparts.

The high frequency component of the pulse is however attenuated by additional resistance due to the skin effect and dielectric loss tangent associated with the PCB material.

In a point-to-point topology, the signal is routed from the transmitter directly to the receiver (this is applied in PCIe, RapidIO, Gigabit Ethernet, DDR2/DDR3/DDR4 DQ/DQS etc.).

A point-to-point topology has the least SI-problems since there is no large impedance matches being introduced by line T's (a two-way split of a trace).

In selecting which tool is best for a particular task, one must consider characteristics of each such as capacity (how many nodes or elements), performance (simulation speed), accuracy (how good are the models), convergence (how good is the solver), capability (non-linear versus linear, frequency dependent versus frequency independent etc.