Complex programmable logic device

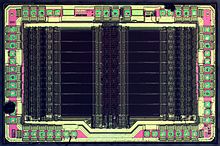

A complex programmable logic device (CPLD) is a programmable logic device with complexity between that of PALs and FPGAs, and architectural features of both.

Some of the CPLD features are in common with PALs: Other features are in common with FPGAs: The most noticeable difference between a large CPLD and a small FPGA is the presence of on-chip non-volatile memory in the CPLD, which allows CPLDs to be used for "boot loader" functions, before handing over control to other devices not having their own permanent program storage.

A good example is where a CPLD is used to load configuration data for an FPGA from non-volatile memory.

[1] CPLDs were an evolutionary step from even smaller devices that preceded them: PLAs (first shipped by Signetics) and PALs.

The main distinction between FPGA and CPLD device architectures is that CPLDs are internally based on a collection of PLDs accompanied by a programmable interconnection structure, while FPGAs use logic blocks.