Intel QuickPath Interconnect

[4] QPI was replaced by Intel Ultra Path Interconnect (UPI) in Skylake-SP Xeon processors based on LGA 3647 socket.

QPI bandwidths are advertised by computing the transfer of 64 bits (8 bytes) of data every two clock cycles in each direction.

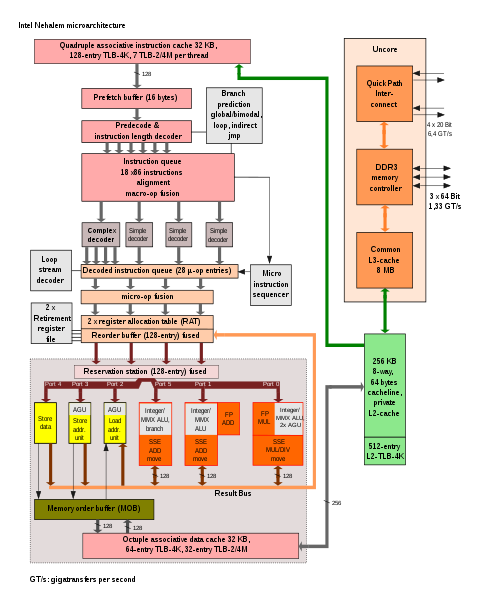

[8] The initial Nehalem implementation used a full four-quadrant interface to achieve 25.6 GB/s (6.4GT/s × 1 byte × 4), which provides exactly double the theoretical bandwidth of Intel's 1600 MHz FSB used in the X48 chipset.

However, QPI is used internally on these chips to communicate with the "uncore", which is part of the chip containing memory controllers, CPU-side PCI Express and GPU, if present; the uncore may or may not be on the same die as the CPU core, for instance it is on a separate die in the Westmere-based Clarkdale/Arrandale.

[13][14][15][16]: 3 In post-2009 single-socket chips starting with Lynnfield, Clarksfield, Clarkdale and Arrandale, the traditional northbridge functions are integrated into these processors, which therefore communicate externally via the slower DMI and PCI Express interfaces.

However, Intel then doubles the result because the unidirectional send and receive link pair can be simultaneously active.

Thus, Intel describes a 20-lane QPI link pair (send and receive) with a 3.2 GHz clock as having a data rate of 25.6 GB/s.

The rate is computed as follows: QPI is specified as a five-layer architecture, with separate physical, link, routing, transport, and protocol layers.