NAND logic

In the field of digital electronic circuits, this implies that it is possible to implement any Boolean function using just NAND gates.

A similar case applies to the NOR function, and this is referred to as NOR logic.

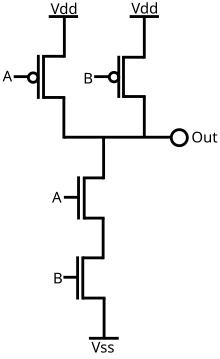

In CMOS logic, if both of the A and B inputs are high, then both the NMOS transistors (bottom half of the diagram) will conduct, neither of the PMOS transistors (top half) will conduct, and a conductive path will be established between the output and Vss (ground), bringing the output low.

If either of the A or B inputs is low, one of the NMOS transistors will not conduct, one of the PMOS transistors will, and a conductive path will be established between the output and Vdd (voltage source), bringing the output high.

As the only configuration of the two inputs that results in a low output is when both are high, this circuit implements a NAND (NOT AND) logic gate.

If the truth table for a NAND gate is examined or by applying De Morgan's laws, it can be seen that if any of the inputs are 0, then the output will be 1.

This construction entails a propagation delay three times that of a single NAND gate.

Alternatively, an XOR gate is made by considering the disjunctive normal form

[1] A demultiplexer performs the opposite function of a multiplexer: It takes a single input and channels it to one of two possible outputs according to a selector bit that specifies which output to choose.