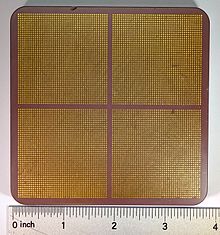

POWER5

The principal improvements are support for simultaneous multithreading (SMT) and an on-die memory controller.

The POWER5 competed in the high-end enterprise server market, mostly against the Intel Itanium 2 and to a lesser extent, the Sun Microsystems UltraSPARC IV and the Fujitsu SPARC64 V. It was superseded in 2005 by an improved iteration, the POWER5+.

The addition of two-way multithreading required the duplication of the return stack, program counter, instruction buffer, group completion unit and store queue so that each thread may have its own.

As many resources such as the register files are shared by two threads, they are increased in capacity in many cases to compensate for the loss of performance.

The unified L3 cache was brought on-package instead of located externally in separate chips.

It uses high-frequency serial buses to communicate with external buffers that interface the dual inline memory modules (DIMMs) to the microprocessor.

It is fabricated by IBM in a 0.13 μm silicon on insulator (SOI) complementary metal–oxide–semiconductor (CMOS) process with eight layers of copper interconnect.

Improvements initially were lower power consumption, due to the newer process it was fabricated in.