Pass transistor logic

[2] If several devices are chained in series in a logic path, a conventionally constructed gate may be required to restore the signal voltage to the full value.

[3] XOR has the worst-case Karnaugh map—if implemented from simple gates, it requires more transistors than any other function.

[5] Other authors use the term "complementary pass transistor logic" (CPL) to indicate a style of implementing logic gates where each gate consists of a NMOS-only pass transistor network, followed by a CMOS output inverter.

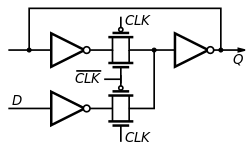

[citation needed] CPL uses series transistors to select between possible inverted output values of the logic, the output of which drives an inverter The CMOS transmission gates consist of nMOS and pMOS transistor connected in parallel.

Static and dynamic types of pass transistor logic exist, with differing properties with respect to speed, power and low-voltage operation.