Technology CAD

Although the emphasis here is on metal oxide semiconductor (MOS) transistors—the workhorse of the IC industry—it is useful to briefly overview the development history of the modeling tools and methodology that has set the stage for the present state-of-the-art.

In the 1970s and 1980s NMOS was favored owing to speed and area advantages, coupled with technology limitations and concerns related to isolation, parasitic effects and process complexity.

[7] It was also during this period that TCAD reached maturity in terms of realizing robust process modeling (primarily one-dimensional) which then became an integral technology design tool, used universally across the industry.

This third generation of TCAD tools became critical to address the full complexity of twin-well CMOS technology (see Figure 3a), including issues of design rules and parasitic effects such as latchup.

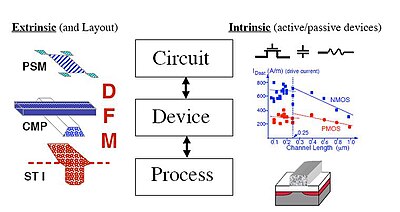

[13] Today the requirements for and use of TCAD cross-cut a very broad landscape of design automation issues, including many fundamental physical limits.

This broad range of issues at the device and interconnect levels, including links to underlying patterning and processing technologies, is summarized in Figure 1 and provides a conceptual framework for the discussion that now follows.

Also shown is the extraction and electrical rule checking (ERC); this indicates that many of the details that to date have been embedded in analytical formulations, may in fact also be linked to the deeper TCAD level in order to support the growing complexity of technology scaling.

The open source GSS,[15] Archimedes,[16] Aeneas,[17] NanoTCAD ViDES, DEVSIM,[18] GMPT and GENIUS have some of the capabilities of the commercial products.